Primary Visual Cortex And Visual Awareness-PDF Free Download

processors support a significantly larger physical memory address space as compared to Cortex-M processors. This section discusses two approaches to address these differences at the system level. TABLE III. ADDRESS SPACE DIFFERENCES BETWEEN CORTEX-A AND CORTEX-M PROCESSORS Cortex-A Cortex-M Physical addressing ARMv7-A: Upto 40-bits

67Mosaico Cortex Honey 30x30 - 12”x12” Mosaico Cortex White 30x30 - 12”x12” 10mm 15x90 - 6”x36” 45x45 - 18”x18” 30x60 - 12”x24” BROWN GREY Gres porcellanato / porcelain feinsteinzeuG / Grès cérame / Керамогранит CORTEX 50 Cortex Brown 4545 Cortex Brown 3060 54 Cortex Brown

geometry of the horizontal connectivity in the primary visual cortex, Journal of Physiology - Paris 103 (2009) 3{45 Matilde Marcolli and Doris Tsao Contact Geometry of the Visual Cortex. Columnar Structure another type of geometric structure present in visual cortex V1 . (from Nakahara, G

Organization of the Cerebral Cortex: Contains up to six distinct layers of cell bodies that are parallel to the surface of the cortex. Cells of the cortex are also divided into columns that lie perpendicular to the laminae. Divided into five lobes: occipital, parietal, temporal, limbic, and frontal. Each part of the cerebral cortex receives specialized input from a particular

E2 Series VS ARM Cortex-M E2 Series VS ARM Cortex-M Comparison Table E2 Series Options E20 Standard Core E21 Standard Core Cortex-M0 Cortex-M3 Cortex-M4 Dhrystone Up to 1.38 DMIPS/MHz 1.1 DMIPS/MHz 1.38 DMIPS/MHz 0.95 DMIPS/MHz 1.25 DMIPS/MHz 1.25DMIPS/MHz CoreMark Up to 3.1 2.4 CoreMarks/MHz 3.1 CoreMarks/MHz 1.8 CoreMarks/MHz 2.76 Coremarks .

Cortex-M4 Technical Reference Manual, ARM DDI0337G, ARM Ltd. ARMv7-M Architecture Reference Manual, ARM DDI0403D, ARM Ltd. . Since the Cortex-M3 is used as the reference, the Cortex-M4 performance is calculated by taking the reciprocal of its relative cycle count. As an example, for the PID function, .

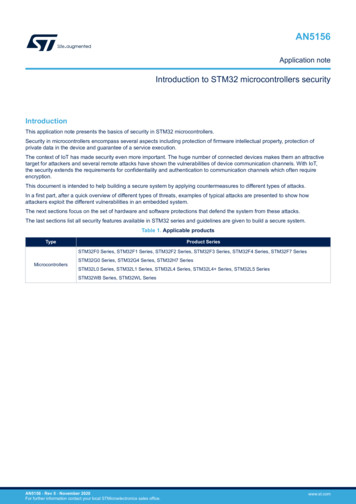

A programming manual is also available for each Arm Cortex version and can be used for MPU (memory protection unit) description: STM32 Cortex -M33 MCUs programming manual (PM0264) STM32F7 Series and STM32H7 Series Cortex -M7 processor programming manual (PM0253) STM32 Cortex -M4 MCUs and MPUs programming manual (PM0214)

STM32 and ultra‑low‑power. 4 9 product series – more than 40 product lines . proliferation of hardware IPs and higher‑level programming languages greatly facilitates the work of developers. High‑ performance Cortex‑M STM32 F7 Ultra‑ low‑power Mainstream Cortex‑M3 STM32 F2 STM32 L1 STM32 F1 Cortex‑M STM32 F4 STM32 L4 STM32 F3 Cortex‑M M STM32 L0 STM32 F0 STM32 H7 ST .

32-bit ARM Cortex-M0 , Cortex-M3 and Cortex-M4 microcontrollers for: Energy, gas, water and smart metering . the EFM32WG Reference Manual. A block diagram of the EFM32WG842 is shown in Figure 2.1 (p. 3) . Figure 2.1. Block Diagram . The EFM32 implementation of the Cortex-M4 is described in detail in A

While the majority of Cortex -M processor-based microcontrollers are single core designs, some new microcontrollers with multiple Cortex-M processors are also available. As multi-core designs are increasing in popularity and complexity, the methodologies of designing multi-core Cortex-M systems are becoming more critical.

The ARM Cortex-M family now has eight processors. In this paper, we compare the features of various Cortex-M processors and highlight considerations for selecting the correct processor for your application. The paper includes detailed comparisons of the Cortex-M instruction sets and advanced interrupt capabilities, along with system-level

Application Cortex-M CMSIS-NN Open Source: launched 23 Jan’18 CMSIS-NN has the equivalent role for Cortex-M CPUs as Compute Library has for Cortex-A and Mali But flow is entirely offline, creating a binary targeting M-class platform DSP instructions in Cortex-M4, M33, M7 &

Single-precision float has been available in Cortex-M processors for quite a long time. When compared to the Cortex-M4 processor, single-precision floating-point support was enhanced (was FPv4 in Cortex-M4, now FPv5 in recent Cortex-M processors), and the performance of single-precision floating-point processing is significantly better.

Qualcomm Quad-core Krait 400/ Quad-core Krait 400/ Quad-core Krait 450 Adreno 330 GPU/ Adreno 330 GPU/ Adreno 420 Snapdragon 808 / Snapdragon 810 Qualcomm 2 4 cores: Cortex-A57 Cortex-A53/ 4 4 cores: Cortex-A57 Cortex-A53 Adreno 418/ Adreno 430 Snapdragon S4 Qualcomm

Arm dual Cortex -A7 800 MHz Cortex -M4 MPU, 3D GPU, TFT/DSI, 37 comm. interfaces, 29 timers, adv. analog, crypto Datasheet -production data Features Includes ST state-of-the-art patented technology Core 32-bit dual-core Arm Cortex -A7 – L1 32-Kbyte I / 3

Raspberry PI Boot (2/2) VideoCore (GPU) SDRAM I/O Cortex A53 Cortex A53 Cortex A53 Cortex A53 Local IO L2 Firmware 3.GPU starts the cores (*) Note: Boot process is very safe - you cannot brick the board. Files on the SD Card (FAT32)

Time frequency analysis Analysis of transient oscillatory activity Examples: auditory cortex / motor cortex Event related synchronization vs. desynchronization Spoken sentence, auditory cortex responses (Fontolan, Morillon et al, 2014) Build up of choice predictive activity in motor cortex

Brain Inspired Information Processing Brain inspired information processing relies on two main operators Pattern detection Probabilistic inference Multiple stages in human sensory processing Primary sensory cortex detects a specific input (i.e. contour, color, or pitch, etc.) Association cortex combines information from primary sensory cortex to produce perception

Copyright 2010 Pearson Education, Inc. Figure 12.8a Functional and structural areas of the cerebral cortex. Gustatory cortex (in insula) Primary motor cortex

that the ruler has fallen. The visual cortex sends a message to the motor cortex to initiate catching the ruler. The motor cortex sends a message to the spinal cord, which then sends a message to the muscle in the hand/fingers. The final process is the contraction of the muscles as the hand grasps the

of the cortex that are involved in cognition and other higher levels of cortical processing. The cortical mantle is divided by sulci and fissures (grooves) into gyri. There are five anatomical lobes of the cerebral cortex: frontal, parietal, temporal, occipital and insular. A. General Functional Organization

Apr 08, 2020 · Microsoft 365, and Project Cortex builds on top of the Graph to create your knowledge network. Project Cortex powers new user experiences for knowledge and content management –including content integration via Microsoft Search, automated classification

ARM Cortex M - Assembly Programming SWRP141 ARM Cortex M Assembly Programming 13 Summary Programming Accessing memory Logical and shift operations Addition, subtraction, multiplication and divide Stack Functions, parameters Co

through the fracture site and crosses the far cortex. Then drill the near cortex by keeping the 2.8 mm/3.5 mm Thin Drill Guide at the same angle and drill with the 3.5 mm x 5" Quick Release Drill (MS-DC35) to the near cortex, ensuring the drill does not pass the fracture site. Measure for screw length by using the Depth Gauge 6-65 mm (80-0623).

ARM Cortex -M4 32b MCU FPU, up to 512KB Flash, 80KB SRAM, FMC, 4 ADCs, 2 DAC ch., 7 comp, 4 Op-Amp, 2.0-3.6 V Datasheet -production data Features Core: ARM Cortex -M4 32-bit CPU with 72 MHz FPU, single-cycle multiplication and HW division, 90 DMIPS (from CCM), DSP instruction and MPU (memory protection unit) Operating conditions:

2 Motor Modules connected to MOTOR ports 2 and 3 on the VEX Cortex 1 VEXnet Remote Control with 6 AAA Batteries 2 VEXnet USB Adapter Keys A computer with ROBOTC for Cortex 2.3 BETA or higher installed 1 VEX Programming Kit 1 USB A-to-A Cable This document is a guide for downloading and running programs on the VEX Cortex .

Cortex-M4 Technical Reference Manual . The Cortex-M4 processor has an optional Memory Protection Unit (MPU) that permits control of individual regions in memory, enabling applications to utilize multiple privilege levels, separating and protecting code, data and stack on a task-by-task basis. Such requirements are

Cortex-M4 Technical Reference Manual . The Cortex-M4 processor has an optional Memory Protection Unit (MPU) that permits control of individual regions in memory, enabling applications to utilize multiple privilege levels, separating and protecting code, data and stack on a task-by-task basis. Such requirements are

The Joystick must first be paired to the Cortex Microcontroller before they will work using the VEXnet Keys. Pairing requires a USB A-A Cable and a VEX 7.2V Battery. This process must be completed each time you use a Joystick or Cortex with a new mate. A Joystick can only communicate with a Cortex that it has been paired with.

The Cortex-M3 and M4 processors share many common elements including advanced on-chip debug . For example, the Cortex-M core has native serial I/O capabilities that can be . Silicon Labs Rev 1.0 3 used to save energy, simplify development and free up peripherals to be used for other application

ARMv7-M Architecture Reference Manual The Definitive Guide to ARM Cortex -M3 and Cortex -M4 Processors STM32F4xx Cortex-M4 programming manual STM32F407xx Datasheet STM32F4Discovery User Manual STM32F40xxx Reference Manual Application Note 230 This introduc

ARM Advanced Microcontroller Bus Architecture (AMBA ) protocol - AXI3: Third-generation ARM interface - AXI4: Adding to the existing AXI definition (extended bursts, subsets) Cortex is the new family of processors - ARM family is older generation; Cortex is current; MMUs in Cortex processors and MPUs in ARM . ARM Processor Architecture

Mobile computing is gearing up for a drastic change this year with the advent of 64-bit ARM based processors which are expected to provide up to 50% performance improvement over existing 32-bit ARM processors. ARM's new Cortex-A50 processor series based on the ARMv8 architecture includes the Cortex-A53 and Cortex-A57 processors. .

TU0308 Tutorial Revision 2.0 2 2 Introduction This tutorial describes how to create a Cortex-M1 processor system that runs on one of the Fusion embedded and development kit boards provided by Microsemi system-on-chip (SoC) Products Group. This design can be used as a starting point for developing the Cortex-M1 embedded system targeting the

Processor ARM Cortex-A5 Intel Quark SoC X1000 MIPS 24K ARM Cortex-M4 ARM Cortex-M0 ISA ARMv7-A x86 (IA32) MIPS32 ARMv7-M ARMv6-M Clock Frequency 536MHz 400MHz 400MHz 80MHz 48MHz L1 Cache 64KB 16KB 0 64KB - - Main Memory 256MB DD

Quad-core 2.3 GHz Krait 400 16GB 40 46 6.2 5.1.98 32 15.12 10.9.5 2.5.9 2017 Android6 Nexus 6P 4x1.55 GHz Cortex-A53 & 4x2.0 GHz Cortex-A57 32GB 52 53 6.3 5.21 34 17.3 12 2.6 2018 Android7 Nexus 6P 4x1.55 GHz Cortex-A53 &

ARMv7-M Architecture Reference Manual, ARM DDI0403D, ARM Ltd. Cortex Microcontroller Software Interface Standard (see www.onarm.com ). Application Note 179

Architecture Thumb Thumb -2 . Cortex-M3 ARMv7-M Harvard Entire Entire 1 cycle Yes Yes No No Cortex-M4 ARMv7E-M Harvard Entire Entire 1 cycle Yes Yes Yes Optional. Universität Dortmund

A. add paloaltonetworks.com to the SSL Decryption Exclusion list B. enable SSL decryption C. disable SSL decryption D. reinstall the root CA certificate Answer: C Question 4 Which two log types should be configured for firewall forwarding to the Cortex Data Lake for use by Cortex XDR? (Choose two) Options: A. Security Event B. HIP C .

This document should be read in conjunction with the STM32L4x6 reference manual (RM0351). For information on the ARM Cortex -M4 core, please refer to the Cortex -M4 Technical Reference Manual, available from the www.arm.com website. Description STM32L476xx 8/103 DocID027459 Rev 2