HiperPF-4 Family - Power

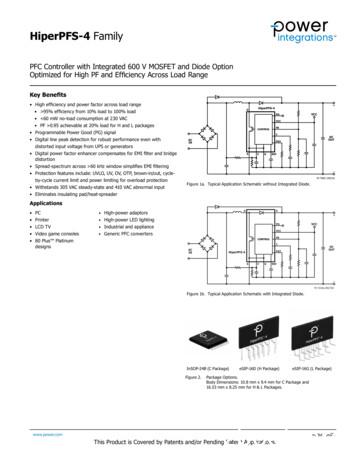

HiperPFS-4 FamilyPFC Controller with Integrated 600 V MOSFET and Diode OptionOptimized for High PF and Efficiency Across Load RangeKey Benefits High efficiency and power factor across load range 95% efficiency from 10% load to 100% load 60 mW no-load consumption at 230 VAC PF 0.95 achievable at 20% load for H and L packages Programmable Power Good (PG) signal Digital line peak detection for robust performance even withdistorted input voltage from UPS or generators Digital power factor enhancer compensates for EMI filter and bridgedistortion Spread-spectrum across 60 kHz window simplifies EMI filtering Protection features include: UVLO, UV, OV, OTP, brown-in/out, cycleby-cycle current limit and power limiting for overload protection Withstands 305 VAC steady-state and 410 VAC abnormal input Eliminates insulating pad/heat-spreaderD 965-100318Figure 1a. Typical Application Schematic without Integrated Diode.Applications PCPrinterLCD TVVideo game consoles80 Plus PlatinumdesignsD High-power adaptorsK High-power LED lightingVCCPG Industrial and applianceVCC Generic PFC -7224a-042720Figure 1b. Typical Application Schematic with Integrated Diode.InSOP-24B (C Package)Figure 2.eSIP-16D (H Package)eSIP-16G (L Package)Package Options.Body Dimensions: 10.8 mm x 9.4 mm for C Package and16.53 mm x 8.25 mm for H & L Packages.www.power.comAugust 2020This Product is Covered by Patents and/or Pending Patent Applications.

PFS7x23-7x29/7633-7636Output Power TableUniversal Input Devices (C Package) Without Integrated DiodeProductContinuous Output Power at 90 VACPFS7623C75 WPFS7624C90 WPFS7626C105 WPFS7628C110 WUniversal Input Devices (H and L Packages)Without Integrated DiodeProductContinuousOutput Power at90 VACPeak Output PowerPFS7623H/L110 W120 WPFS7624H/L130 W150 WPFS7625H/L185 W205 WPFS7626H/L230 W260 WPFS7627H/L290 W320 WPFS7628H/L350 W385 WPFS7629H/L405 W450 WHigh-Line Input Only Devices (H Package)Without Integrated DiodeContinuousOutput Power at180 VACPeak OutputPowerPFS7633H255 W280 WPFS7634H315 W350 WPFS7635H435 W480 WPFS7636H550 W610 WProductUniversal Input Devices With Integrated DiodeProductMaximum ContinuousOutput Power Ratingat 90 VAC(Full Power Mode)Peak Output Power(Full Power Mode)PFS7723L/H110 W120 WPFS7724L/H130 W150 WPFS7725L/H185 W205 W260 WPFS7726H230 WPFS7727H290 W320 WPFS7728H350 W385 WPFS7729H405 W450 WTable 1.Output Power Table (See Table 2 on page 12 for Maximum ContinuousOutput Power Ratings.)2Rev. F 08/20www.power.com

PFS7x23-7x29/7633-7636DescriptionThe HiperPFS -4 devices incorporate a continuous conduction mode(CCM) boost PFC controller, gate driver and 600 V power MOSFET in asingle, low-profile (GROUND pin connected) power package. HiperPFS-4devices eliminate need for external current sense resistors and theirassociated power loss, and use an innovative control technique thatadjusts the switching frequency over output load, input line voltage,and input line cycle.This control technique maximizes efficiency over the entire load range,particularly at light loads. Additionally, it minimizes the EMI filteringrequirements due to its wide bandwidth spread spectrum effect. TheHiperPFS-4 uses advanced digital techniques for line monitoring, linefeed-forward scaling, and power factor enhancement; while usinganalog techniques for the core controller in order to maintain extremelylow no-load power consumption. The HiperPFS-4 also features anintegrated non-linear error amplifier for enhanced load transientresponse, a user programmable Power Good (PG) signal as well as userselectable power limit functionality. HiperPFS-4 includes PowerIntegrations’ standard set of comprehensive protection features, suchas UV, OV, brown-in/out, and hysteretic thermal shutdown. HiperPFS-4also provides cycle-by-cycle current limit and Safe Operating Area(SOA) protection of the power MOSFET, output power limiting foroverload protection, and pin-to-pin short-circuit protectionHiperPFS-4’s innovative variable frequency continuous conductionmode operation (VF-CCM) minimizes switching losses by maintaining alow average switching frequency, while modulating the switchingfrequency in order to suppress EMI, the traditional challenge withcontinuous conduction mode solutions. Systems using HiperPFS-4typically reduce the total X and Y capacitance requirements of theconverter, the inductance of both the boost choke and EMI noisesuppression chokes, thereby reducing overall system size and cost.Additionally, HiperPFS-4 devices dramatically reduce component countand board footprint while simplifying system design and enhancingreliability, when compared with designs that use discrete MOSFETs andcontrollers. The innovative variable frequency, continuous conductionmode controller enables the HiperPFS-4 to realize all of the benefits ofcontinuous conduction mode operation while leveraging low-cost,small, simple EMI filters.Many regions mandate high power factor for many electronic productswith high power requirements. These rules are combined withnumerous application-specific standards that require high power supplyefficiency across the entire load range, from full load to as low as 10%load. High efficiency at light load is a challenge for traditional PFCsolutions where fixed MOSFET switching frequencies cause fixedswitching losses on each cycle, even at light loads. In addition tofeaturing flat efficiency across the load range, HiperPFS-4 also enablesa high power factor of 0.95 at 20% load. HiperPFS-4 simplifiescompliance with new and emerging energy-efficiency standards over abroad market space in applications such as PCs, LCD TVs, notebooks,appliances, pumps, motors, fans, printers and LED lighting.HiperPFS-4’s advanced power packaging technology and highefficiency simplify the complexity of mounting the IC and thermalmanagement, while providing very high power capabilities in a singlecompact package; these devices are suitable for PFC applications withmaximum continuous power from 75 W to 405 W universal (550 Whigh-line only).Product HighlightsProtected Power Factor Correction Solution Incorporates 600 V power MOSFET, controller and gate driver. EN61000-3-2 Class C and Class D compliance. Integrated protection features reduce external component count Accurate built-in brown-in/out protection. Accurate built-in undervoltage (UV) protection.Accurate built-in overvoltage (OV) protection.Hysteretic thermal shutdown (OTP).Internal power limiting function for overload protection.Cycle-by-cycle power-switch current limit.Internal non-linear error amplifier for enhanced load transientresponseNo external current sense resistor required. Provides ‘lossless’ internal sensing via sense-FET. Reduces component count and system losses. Minimizes high current gate drive loop area.Minimizes output overshoot and stresses during start-up Integrated power limit.Improved dynamic response. Digitally controlled input line feed-forward gain adjustment forflattened loop gain across entire input voltage range.Eliminates up to 39 discrete components for higher reliability andlower cost.Solution for High Efficiency, Low EMI and High PF Continuous conduction mode PFC uses novel constant amp-second[on-time] volt-second [off-time] control. High efficiency across load. High power factor across load. Frequency sliding technique for light load efficiency improvements. 95% efficiency from 10% load to full load achievable atnominal input voltages. Variable switching frequency to simplify EMI filter design. Varies over line input voltage to maximize efficiency andminimize EMI filter requirements. Varies with input line cycle voltage by 60 kHz to maximizespread spectrum effect.Advanced Package for High Power Applications(H & L Packages) Up to 450 W [universal], 610 W [high-line only] peak output powercapability in a highly compact package. Simple adhesive or clip mounting to heat sink. No insulation pad required and can be directly connected toheat sink. Staggered pin arrangement allows simple routing of board tracesand to meet high-voltage creepage requirements. Single package solution for PFC converter reduces assembly costsand layout size.SMD Package (C Package) Allows the elimination of metal heat sink. Use PCB copper foil for heat dissipation.Pin Functional DescriptionBIAS POWER (VCC) PinThis is a 10.2-15 VDC [12 V typical] bias supply used to power the IC.The bias voltage must be externally clamped to prevent the BIASPOWER pin from exceeding 15 VDC to ensure long-term reliabilityREFERENCE (REF) PinThis pin is connected to an external bypass capacitor and is used toprogram the IC for either FULL or EFFICIENCY power mode. Theexternal capacitor is connected between the REFERENCE and SIGNALGROUND [G] pins. Note: the return trace to the ground pin must notbe shared with other return traces that may pass large returncurrents during surge events. The REFERENCE pin has two validcapacitor values to select ‘Full’ (1.0 mF 20%) or ‘Efficiency’ (0.1 mF 20%) power modes.SIGNAL GROUND (G) PinDiscrete components used in the feedback circuit, including loopcompensation, decoupling capacitors for the BIAS POWER (VCC),REFERENCE (REF) and VOLTAGE MONITOR (V) must be referenced to3www.power.comRev. F 08/20

PFS7x23-7x29/7633-7636the SIGNAL GROUND (G) pin. The SIGNAL GROUND pin is alsoconnected to the tab of the device. The SIGNAL GROUND pin shouldnot be tied directly to the SOURCE pin external to the IC.VOLTAGE MONITOR (V) PinThe VOLTAGE MONITOR pin is tied to the rectified high-voltage DCrail through a 100:1, 1% high-impedance resistor divider to minimizepower dissipation and standby power consumption. The recommendedresistance value is between 8 MW and 16 MW. Changing this dividerratio affects peak power limit, brown-in/out thresholds and willdegrade input current quality (reduce power factor and increaseTHD). A small ceramic capacitor forming an 80 ms nominal timeconstant must be connected between the VOLTAGE MONITOR pin tothe SIGNAL GROUND pin to bypass any switching noise present onthe rectified DC bus.This pin also features brown-in/out detection thresholds andincorporates a weak current source that acts as a pull-down in theevent of an open circuit condition.COMPENSATION (C) PinThis pin is used for loop pole/zero compensation of the OTA erroramplifier via the connection of a network of capacitors and a resistorbetween the COMPENSATION pin and SIGNAL GROUND pin. TheCOMPENSATION pin connects internally to the output of the OTAerror amplifier and the input to the on-time and off-time controllers.FEEDBACK (FB) PinThis pin is connected to the main voltage regulation feedback resistordivider network and is also used for fast over and undervoltageprotection. This pin also detects the presence of the feedbackvoltage divider network at start-up and during operation. The dividerratio should be the same as the VOLTAGE MONITOR pin for properH Package (eSIP-16D)(Front View)and optimized power limit and power factor. A large upper resistorbetween 8 MW and 16 MW 1% is recommended. A small ceramiccapacitor between FEEDBACK and SIGNAL GROUND, forming anominal 80 ms time-constant with the bottom resistor, is required.POWER GOOD (PG) PinUse of the PG function is optional. The POWER GOOD pin is anactive low, open-drain connection which sinks current when theoutput voltage is in regulation. At start-up, once the FEEDBACK pinvoltage has risen to 95% of the internal reference voltage, thePOWER GOOD pin is asserted low.After start-up, the output voltage threshold at which the PG signalbecomes high-impedance depends on the threshold programmed bythe POWER GOOD THRESHOLD pin resistor. When not used, thePOWER GOOD pin is left unconnected.POWER GOOD THRESHOLD (PGT) PinThis pin is used to program the output voltage threshold at which thePG signal becomes high-impedance representing the PFC stage fallingout of regulation. The low threshold for the PG signal is programmedwith a resistor between the POWER GOOD THRESHOLD and SIGNALGROUND pins. Tying the POWER GOOD THRESHOLD to theREFERENCE pin disables the power good function (i.e. POWER GOODpin remains high impedance).SOURCE (S) PinsThese pins are the source connection of the power switch as well asthe negative bulk capacitor terminal connection.DRAIN (D) PinThis is the drain connection of the internal power switch.Boost Diode Cathode (K) PinThis is the cathode connection of the internal Qspeed diode.H Package (eSIP-16D)(Back View)Pin 1 I.D.GL Package (eSIP-16G)(Front View)Exposed Pad (Backside ofBoth H and L Packages)Internally Connected toGROUND (G) PinGPin 1 I.D.NCS1416NC/K13D9 11PGTS 24SD 16-197FBVCCREFGVCFBPGPGTSSDNCNC/KC Package (InSOP-24B)(Top View)8 10PG15VNC/KNCDSSPGTPGFBCVGREFVCC16 14 13 1110 9 8 7 6 5 4 3NC 13NC 14NC 1536C3 4 5 6 7 8 910 11 1314 16REF14GVCC1Exposed Pad(Backside)Not ShownNote pin 16 is NC for PFS76xx and K pin for PFS772x.C Package (InSOP-24B)(Bottom View)121110987654321GNCNCNCPGTPGFBCVREFGVCCExposed PadConnected toDRAIN (D) PinPI-8616-081320Figure 3.Pin Configuration.4Rev. F 08/20www.power.com

PFS7x23-7x29/7633-7636DRAIN (D)BOOST DIODE CATHODE (K)BIAS POWER (VCC)VOLTAGE MONITOR (V)INPUT LINE INTERFACEVV12 V GATE DRIVERREF SERIES/SHUNTREGULATOR -PEAKDETECTORADCBROWN-IN/OUT DETECTUVLOIntegrated QspeedUltrafast Diode(Diode option in PFS772xH/L only)BO, BIHL/LLMON(PFE)IOCPVCCMOFF (VFB - VV) (VO-VIN)LOW/HIGHLINE DETECTVBRST FBREF VPG(H) FBUV FBOFF FBOVOff-Time ControllerCINTPFENHANCER REFERENCE(REF)IPGTREFERENCEAND BAND GAPPONFEEDBACK PinOV/UV/OFFPowerMOSFETISNSIOCP VCCLatchLEB-TIMERSUPERVISORsenseFET VOFF VOFFVOFF is a function of the error-voltage(VE) and is used to reducethe average operating frequencyas a function of output powerFrequencySlideHL/LLNon-Linear OTA OCP--FBREFFEEDBACK(FB)OTA-POWER LIMITSOA RAMPFeedback UVVBRST-Feedback OFFOn-Time ControllerCINTFBUV-FBOFF PON MON(PFE) ISNSMON(PFE) is the switchcurrent sense scalefactor which is a functionof the peak input voltageBuffer andDe-GlitchFilter HL/LLFBOV VEVEFeedback OVVFB VPG(H)REF-START-UP,FMEA CHECKSSOURCE (S)SIGNAL GROUND (G)IPGTPOWER GOODTHRESHOLD(PGT)POWER GOOD(PG)COMPENSATION (C)PI-7969a-081920Figure 4.Functional Block Diagram.Functional DescriptionThe HiperPFS-4 family are variable switching frequency boost PFCdevices. It employs a constant amp-second on-time and constantvolt-second off-time control algorithm. This algorithm is used toregulate the output voltage and shape the input current to complywith regulatory harmonic current limits (high power factor). Integrating the switch current and controlling it to have a constant amp-secproduct over the on-time of the switch allows the average inputcurrent to follow the input voltage. Integrating the differencebetween the output and input voltage maintains a constant voltsecond balance dictated by the electro-magnetic properties of theboost inductor and thus regulates the output voltage and power.More specifically, the control technique sets constant volt-seconds forthe off-time (tOFF). The off-time is controlled such that: V O -V IN h # t OFF K 1(1)(2)Since the volt-seconds during the on-time must equal the voltseconds during the off-time, to maintain flux equilibrium in the PFCchoke, the on-time (tON) is controlled such thatV IN # t ON K 1The controller also sets a constant value of charge delivered duringeach on-cycle of the power MOSFET. The charge per cycle is variedgradually over many switching cycles in response to load changes soit can be considered constant for a half line cycle. With this constantcharge (or amp-second) control, the following relationship is thereforealso true:I IN # t ON K 2Substituting tON from (2) into (3) gives:I IN V IN # K 2(3)(4)K1The relationship of (4) demonstrates that by controlling a constantamp-second on-time and constant volt-second off-time, the inputcurrent IIN is proportional to the input voltage VIN, therefore providingthe fundamental requirement of power factor correction.This control produces a continuous mode power switch currentwaveform that varies both in frequency and peak current value acrossa line half-cycle to produce an input current proportional to the inputvoltage.5www.power.comRev. F 08/20

PFS7x23-7x29/7633-7636Control EngineThe controller features a low bandwidth, high gain OTA error-amplifierof which its non-inverting terminal is connected to an internal voltagereference of 3.85 V. The inverting terminal of the error-amplifier isavailable on the external FEEDBACK pin which connects to the outputvoltage divider network with a divider ratio of 1:100 to regulate theoutput voltage to 385 V nominally. The FEEDBACK pin connectsdirectly to the divider network for fast transient load response.The internally sensed FET switch current is scaled by the inputvoltage peak detector current sense gain (MON) then integrated andcompared with the error-amplifier signal (VE) to determine the cycleon-time. Internally the difference between the input and outputvoltage is derived and the resultant is scaled, integrated, andcompared to a voltage reference (VOFF) to determine the cycle off-time.Careful selection of the internal scaling factors produce input currentwaveforms with very low distortion and high power factor.Line Feed-Forward Scaling Factor (MON) and PF EnhancerThe VOLTAGE MONITOR (V) pin voltage is sampled and converted bya Δ-Σ ADC to a quantized digital value. A digital line cycle peakdetector, with dynamic time constants and multi-cycle filtering,derives and smooths the peak of the input line voltage. This peak isused internally to scale the gain of the current sense signal throughthe MON variable. This contribution is required to reduce the dynamicrange of the control feedback signal as well as flatten the loop gainover the operating input line range. The line-sense feed-forward gainadjustment is proportional to the square of the peak rectified AC linevoltage and is adjusted as a function of the VOLTAGE MONITOR pinvoltage.At high-line and light load, the feed-forward MON variable is dynamically adjusted across the line cycle in order to compensate for the linecurrent distortion through the EMI filter and full bridge network, andimprove power factor.VELatchRESETIS dtVOFFLatchSET(VOUT-VIN)dtGateDrive (Q)MaximumON-timeMinimumOFF-timeFigure 5.TimingSupervisorPI-5335-061615The line-sense feed-forward gain is also important in providing aswitch power limit over the input line range.This characteristic is optimized to maintain a relatively constantinternal error-voltage level at full load from an input line of 90 to230 VAC.Beyond the specified peak power rating of the device, the internalpower limit will regulate the output voltage below the set regulationthreshold as a function of output overload to maintain constantoutput power. Figure 6 illustrates the typical regulation characteristicas a function of load.Below the brown-in threshold (VBR ) the power limit is reduced whenthe device is operated in the ‘Full’ power mode as shown in Figure 7.As the input line voltage is reduced toward the brown-out threshold(VBR-) and if the load exceeds the power limit derating, the boostoutput voltage will drop out of regulation in accordance with Figure 6.The rated peak power shown in Table 1 is not derated for voltagesbelow the brown-in threshold when the device is operated in the‘Efficiency’ mode.Start-Up with Pin-to-Pin Short-Circuit ProtectionAt start-up, the engine performs a sequence of operational checksand pin short/open evaluations, as shown in Figure 8, prior to thecommencement of switching. When the input voltage peak is abovebrown-in, the engine enables switching.The OTA error amplifier provides a non-linear amplifier (NLA)mechanism to overcome the inherently slow feedback loop responsewhen the sensed output voltage on the FEEDBACK pin is outside itsregulation window. This allows the error amplif

S D C PGT FB VCC PG V G REF CONTROL HiperPFS-4 VCC Figure 2. Package Options. Body Dimensions: 10.8 mm x 9.4 mm for C Package and 16.53 mm x 8.25 mm for H & L Packages. InSOP-24B (C Package) eSIP-16D (H Package) eSIP-16G (L Package) CONTROL PI-7224a-042720 AC IN DC OUT

Catan Family 3 4 4 Checkers Family 2 2 2 Cherry Picking Family 2 6 3 Cinco Linko Family 2 4 4 . Lost Cities Family 2 2 2 Love Letter Family 2 4 4 Machi Koro Family 2 4 4 Magic Maze Family 1 8 4 4. . Top Gun Strategy Game Family 2 4 2 Tri-Ominos Family 2 6 3,4 Trivial Pursuit: Family Edition Family 2 36 4

Story – Talk of the Block Family SV, “Kim and the Kids,” pg 9-10 Volunteer’s family pictures (if possible) Family worksheet (see below) Activity Ideas: Family tree: T introduces family by talking about own family and drawing a very simplified family tree on the board using the family vocabulary words (see above). Feel free to bring

Gateway Math & English Completion in 1. st. . FAMILY FEUD FAMILY FEUD FAMILY FEUD FAMILY FEUD FAMILY FEU FAMILY FEUD FAMILY FEUD FAMILY FEUD FAMILY FEUD FAMILY FE. National Center for Inquiry & Improvement www.ncii -improve.com Round 1: What Do New Students Ask .

A. Family Office Detailed Background Data B. Family Office Investment Objectives and Asset Management C. Family Office Risk and Return Measurements D. Family Office Governance E. Family Office Documentation F. Family Office Processes G. Family Office Communications H. Family Office Human Resources Practices I. Family Office Education and .

WHAT IS A FAMILY OFFICE? TYPES OF FAMILY OFFICES A single family office (SFO) is a family office serving (multiple) generations of one single wealthy family. The SFO is designed to fit the specific needs and beliefs of the family. A public multi-family office (MFO) is a family office looking after interests of multiple families with less wealth.

N6700 Modular Power System Family Data Sheet Low-Proile Mainframes for ATE: N6700B, N6701A, N6702A DC Power Analyzer Mainframe for R&D: N6705B DC Power Modules: N6731B - N6784A Software for DC Power: 14585A. N6700 Modular Power System Family Overview Create a power system that

Prevention and Family Recovery Advancing the Capacity of Family Drug Courts to Provide a Comprehensive Family-Centered Approach to Improve Child, Parent and Family Outcomes Family-centered services that focus on parent-child relationships are a critical ingredient of effective family drug courts (FDCs).1 The Prevention and Family

Achieved a high qualification In Radiology such as American Board, ABRMI or equivalent. Has an experience of at least 3 years after the higher qualification. Of the rank of Consultant Radiologist. Is employed on a full time basis , in the selected training hospital/ center -6-4.2 - Responsibilities and Duties of the Trainer Responsible for the actual performance of the trainee. Look after the .