Basic Computer Organization And Design

Basic Computer Organization and DesignPart 3/3Adapted byDr. Adel AmmarComputer Organization

Interrupt Initiated Input/Output Open communication only when some data has to be passed -- interrupt. The I/O interface, instead of the CPU, monitors the I/O device. When the interface founds that the I/O device is ready for datatransfer, it generates an interrupt request to the CPU Upon detecting an interrupt, the CPU stops momentarily the task itis doing, branches to the service routine to process the datatransfer, and then returns to the task it was performing. IEN (Interrupt-enable flip-flop) can be set and cleared by instructions when cleared, the computer cannot be interruptedComputer Organization2

Flowchart for Interrupt CycleR Interrupt F/F 0Instruction cycleInterrupt cycle 0IEN 1 1 1Store return addressin location 0M[0] PCFetch and decodeinstructionsExecuteinstructionsRBranch to location 1PC 1FGI 0 1IEN 0R 0FGO 0R 1vvvvThe interrupt cycle is a HW implementation of a branch and save return address operation.At the beginning of the next instruction cycle, the instruction that is read from memory is in address 1.At memory address 1, the programmer must store a branch instruction that sends the control to aninterrupt service routineThe instruction that returns the control to the original program is "indirect BUN 0"Computer Organization3

Register Transfer Microoperations in InterruptCycleMemoryBefore interrupt010BUN1120MainProgram255PC 2561120After interrupt cycle0PC 1 rogram01BUN0 Register Transfer Statements for Interrupt Cycle R F/F 1 if IEN (FGI FGO)T0 T1 T2 T0 T1 T2 (IEN)(FGI FGO): R 1 The fetch and decode phases of the instruction cycle must be modified ReplaceT0, T1, T2 with R'T0, R'T1, R'T2 The interrupt cycle : RT0: RT1: RT2:AR 0, TR PCM[AR] TR, PC 0PC PC 1Computer Organization4

Complete Computer DescriptionFlowchart of OperationsstartSC 0, IEN 0, R 0 0(InstructionCycle)R’T0AR PCR’T1IR M[AR], PC PC 1R’T2AR IR(0 11), I IR(15)D0.D7 Decode IR(12 14) 1(Register or I/O) 1 (I/O)D7IT3ExecuteI/OInstructionI 0 (Register)D7I’T3ExecuteRRInstructionR 1(InterruptCycle)RT0AR 0, TR PCM[AR] TR, PC 0RT1PC PC 1, IEN 0R 0, SC 0D7RT2 0(Memory Ref) 1(Indir)D7’IT3AR - M[AR]I 0(Dir)D7’I’T3IdleExecute MRInstructionComputer OrganizationD7’T45

Further Questions on Interruptv How can the CPU recognize the device requesting aninterrupt ?v Since different devices are likely to require different interruptservice routines, how can the CPU obtain the startingaddress of the appropriate routine in each case ?v Should any device be allowed to interrupt the CPU whileanother interrupt is being serviced ?v How can the situation be handled when two or moreinterrupt requests occur simultaneously ?Computer Organization6

Complete Computer DescriptionMicrooperationsFetchDecodeR T0:R T1:R T2:IndirectD7 IT3:InterruptT0 T1 T2 (IEN)(FGI :ISZD6T4:D6T5:D6T6:AR PCIR M[AR], PC PC 1D0, ., D7 Decode IR(12 14),AR IR(0 11), I IR(15)AR M[AR]R 1AR 0, TR PCM[AR] TR, PC 0PC PC 1, IEN 0, R 0, SC 0DR M[AR]AC AC DR, SC 0DR M[AR]AC AC DR, E Cout, SC 0DR M[AR]AC DR, SC 0M[AR] AC, SC 0PC AR, SC 0M[AR] PC, AR AR 1PC AR, SC 0DR M[AR]DR DR 1M[AR] DR, if(DR 0) then (PC PC 1),SC 0Computer Organization7

Complete Computer DescriptionMicrooperationsRegister-ReferenceD7I T3 rIR(i) utD7IT3 pIR(i) ommon to all register-reference instr)(i 0,1,2, ., 11)SC 0AC 0E 0AC AC E E AC shr AC, AC(15) E, E AC(0)AC shl AC, AC(0) E, E AC(15)AC AC 1If(AC(15) 0) then (PC PC 1)If(AC(15) 1) then (PC PC 1)If(AC 0) then (PC PC 1)If(E 0) then (PC PC 1)S 0(Common to all input-output instructions)(i 6,7,8,9,10,11)SC 0AC(0-7) INPR, FGI 0OUTR AC(0-7), FGO 0If(FGI 1) then (PC PC 1)If(FGO 1) then (PC PC 1)IEN 1IEN 0Computer Organization8

Design of Basic ComputervvvHardware Components of Basic ComputerA memory unit: 4096 x 16.Registers:ðvFlip-Flops (Status):ðvAR, PC, DR, AC, IR, TR, OUTR, INPR, and SCI, S, E, R, IEN, FGI, and FGODecoders:ðða 3x8 Opcode decodera 4x16 timing decodervvvCommon bus: 16 bitsControl logic gates:Adder and Logic circuit: Connected to ACvControl Logic Gates- Input Controls of the nine registers- Read and Write Controls of memory- Set, Clear, or Complement Controls of the flip-flops- S2, S1, S0 Controls to select a register for the bus- AC, and Adder and Logic circuitComputer Organization9

Control of Registers and Memoryv Address Register: ARð Scan all of the register transferstatements that change thecontent of AR:R’T0:R’T2:D’7IT3:RT0:D5T4:AR PCLD(AR)AR IR(0-11) LD(AR)AR M[AR]LD(AR)AR 0CLR(AR)AR AR 1INR(AR)LD(AR) R'T0 R'T2 D'7IT3CLR(AR) RT0INR(AR) D5T4T2D'7IT3From bus1212ARTo busClockLDINRCLRRT0D5T4Computer Organization10

Control of Flagsv IEN: Interrupt Enable Flagð pB7: IEN 1 (I/O Instruction)ð pB6: IEN 0 (I/O Instruction)ð RT2: IEN 0 (Interrupt)ð p D7IT3 (Input/Output Instruction)D7IT3pB7B6JQIENKRT2Computer Organization11

Control of Common Busx1x2x3x4x5x6x7S2EncoderS1bus selectinputsS0x1 x2 x3 x4 x5 x6 x701000000For 01000000001S2 S1 DRACIRTRMemoryD4T4: PC ARD5T5: PC ARx1 D4T4 D5T5Computer Organization12

Design of Accumulator LogicCircuits associated with AC1616From DRFrom INPR8Adder andlogiccircuit16To busLDAll the statements that change ACD0T5:D1T5:D2T5:pB11:rB9:rB7 :rB6 :rB11 :rB5 :16ACINRCLRClockControlgatesAC AC DRAND with DRAC AC DRAdd with DRAC DRTransfer from DRAC(0-7) INPRTransfer from INPRAC AC ComplementAC shr AC, AC(15) E Shift rightAC shl AC, AC(0) EShift leftAC 0ClearAC AC 1IncrementComputer Organization13

Control of AC RegisterGate structures for controllingthe LD, INR, and CLR of ACFrom Adderand LogicD0T5D1ANDD2T5pB11rB9DRB7B6B5ADD1616ACTo busClockLDINRCLRINPRCOMSHRSHLINCCLRB11Computer Organization14

ALU (Adder and Logic Circuit)One stage of Adder and Logic circuitDR(i)AC(i)ANDCiIiFAC i 1FromINPRbit(i)LDADDJQAC(i)DRKINPRCOMSHRAC(i 1)SHLAC(i-1)Computer Organization15

Announcementsv Readingsð Chapter 5 of the textbook: Computer System Architecture, M. Manoð 5-3, 5-4, 5-6, 5-9, 5-10, 5-11, 5-12, 5-15, 5-16, 5-17, 5-18Computer Organization16

Computer Organization 3 Flowchart for Interrupt Cycle v The interrupt cycle is a HW implementation of a branch and save return address operation. v At the beginning of the next instruction cycle, the instruction that is read from memory is in address 1. v At memory address 1, the programmer must st

1.1 BASIC COMPUTER ORGANIZATION: Most of the computer systems found in automobiles and consumer appliances to personal computers and main frames have some basic organization. The basic computer organization has three main components: CPU Memory subsystem I/O subsystem. The generic organization of these components is shown in the figure below .

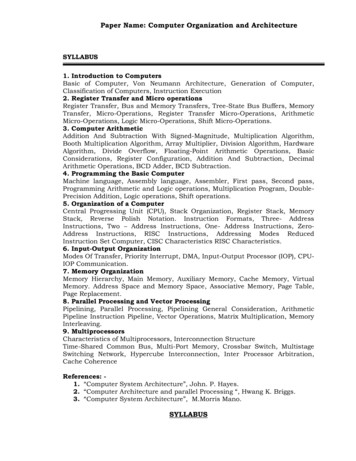

Paper Name: Computer Organization and Architecture SYLLABUS 1. Introduction to Computers Basic of Computer, Von Neumann Architecture, Generation of Computer, . “Computer System Architecture”, John. P. Hayes. 2. “Computer Architecture and parallel Processing “, Hwang K. Briggs. 3. “Computer System Architecture”, M.Morris Mano.

need to explore when you look at organization design. Many people equate organization design with an organization's structure: The words "lean" and "flat" are used to describe organization design as well as it's structure. In fact, organizational design encompasses much more than simply the structure: Organization design is the process of .

CS31001 COMPUTER ORGANIZATION AND ARCHITECTURE Debdeep Mukhopadhyay, CSE, IIT Kharagpur References/Text Books Theory: Computer Organization and Design, 4th Ed, D. A. Patterson and J. L. Hennessy Computer Architceture and Organization, J. P. Hayes Computer Architecture, Berhooz Parhami Microprocessor Architecture, Jean Loup Baer

1. Computer Fundamentals by P.K.Sinha _ Unit I: Introduction to Computers: Introduction, Definition, .Characteristics of computer, Evolution of Computer, Block Diagram Of a computer, Generations of Computer, Classification Of Computers, Applications of Computer, Capabilities and limitations of computer. Unit II: Basic Computer Organization:

CAD/CAM Computer-Aided Design/Computer-Aided Manufacturing CADD Computer-Aided Design and Drafting CADDS Computer-Aided Design and Drafting System CADE Computer-Aided Design Equipment CADEX Computer Adjunct Data Evaluator-X CADIS Communication Architecture for Distributed Interactive Simulation CADMAT Computer-Aided Design, Manufacture and Test

COMPUTER ORGANIZATION (3-1-0 ) . Computer System Architecture, Morris Mano, PHI Reference Books: 1. Computer Architecture & Organization, William Stallings, Pearson Prerequisite 1. Knowledge of digital circuit 2. Functionality of various gates . Computer Architecture and Organization, by - John P. Hayes, 3rd Edition, Mc Graw Hill .

Autumn 2010 CSE370 - XIX - Computer Organization 1 Computer organization Computer design – an application of digital logic design procedures Computer processing unit memory system Processing unit control datapath Control finite state machine inputs machine instruction, datapath conditions outputs register transfer control signals, ALU operation codes