Guide: Logic Simulation - Xilinx

See all versionsof this documentVivado Design Suite UserGuide: Logic SimulationUG900 (v2020.1) June 3, 2020

Revision HistoryRevision HistoryThe following table shows the revision history for this document.Revision SummarySection06/03/2020 Version 2020.1Chapter 3: Simulating with Third-Party SimulatorsAdded table 8 and table 9General UpdatesUpdated Using Simulation Settings in chapter 2General UpdatesUpdated Object Windows in chapter 4UG900 (v2020.1) June 3, 2020Vivado Design Suite User Guide: Logic SimulationSend Feedbackwww.xilinx.com2

Table of ContentsRevision History.2Chapter 1: Logic Simulation Overview. 7Supported Simulators.7Simulation Flow . 8Language and Encryption Support . 11Chapter 2: Preparing for Simulation.12Using Test Benches and Stimulus Files. 12Pointing to the Simulator Install Location. 13Compiling Simulation Libraries. 14Using Xilinx Simulation Libraries.19Using Simulation Settings. 28Adding or Creating Simulation Source Files. 32Generating a Netlist. 34Chapter 3: Simulating with Third-Party Simulators. 37Running Simulation Using Third Party Simulators with Vivado IDE. 39Dumping SAIF for Power Analysis.42Dumping VCD. 44Simulating IP.45Using a Custom DO File During an Integrated Simulation Run. 45Running Third-Party Simulators in Batch Mode.48Chapter 4: Simulating with Vivado Simulator. 49Running the Vivado Simulator.49Running Functional and Timing Simulation.67Saving Simulation Results. 69Distinguishing Between Multiple Simulation Runs.70Closing a Simulation. 70Adding a Simulation Start-up Script File.71Viewing Simulation Messages. 72Using the launch simulation Command. 73UG900 (v2020.1) June 3, 2020Vivado Design Suite User Guide: Logic SimulationSend Feedbackwww.xilinx.com3

Re-running the Simulation After Design Changes (relaunch). 74Using the Saved Simulator User Interface Settings.75Chapter 5: Analyzing Simulation Waveforms with VivadoSimulator. 77Using Wave Configurations and Windows. 77Opening a Previously Saved Simulation Run. 78Understanding HDL Objects in Waveform Configurations .79Customizing the Waveform. 82Controlling the Waveform Display . 88Organizing Waveforms.92Analyzing Waveforms. 94Analyzing AXI Interface Transactions. 99Chapter 6: Debugging a Design with Vivado Simulator. 114Debugging at the Source Level. 114Forcing Objects to Specific Values.118Power Analysis Using Vivado Simulator. 126Using the report drivers Tcl Command.128Using the Value Change Dump Feature. 128Using the log wave Tcl Command. 129Cross Probing Signals in the Object, Wave, and Text Editor Windows. 131Chapter 7: Simulating in Batch or Scripted Mode in VivadoSimulator.137Exporting Simulation Files and Scripts. 137Running the Vivado Simulator in Batch Mode.143Elaborating and Generating a Design Snapshot, xelab.145Simulating the Design Snapshot, xsim.156Example of Running Vivado Simulator in Standalone Mode. 159Project File (.prj) Syntax.160Predefined Macros. 161Library Mapping File (xsim.ini). 161Running Simulation Modes.162Using Tcl Commands and Scripts .165export simulation .166export ip user files.169UG900 (v2020.1) June 3, 2020Vivado Design Suite User Guide: Logic SimulationSend Feedbackwww.xilinx.com4

Appendix A: Compilation, Elaboration, Simulation, Netlist, andAdvanced Options. 171Compilation Options.171Elaboration Options. 174Simulation Options. 175Netlist Options.178Advanced Simulation Options. 178Appendix B: SystemVerilog Support in Vivado Simulator. 180Targeting SystemVerilog for a Specific File. 180Testbench Feature.187Appendix C: Universal Verification Methodology Support. 196Appendix D: VHDL 2008 Support in Vivado Simulator. 197Introduction . 197Compiling and Simulating.197Supported Features. 199Appendix E: Direct Programming Interface (DPI) in VivadoSimulator.202Introduction. 202Compiling C Code.202xsc Compiler. 203Binding Compiled C Code to SystemVerilog Using xelab. 204Data Types Allowed on the Boundary of C and SystemVerilog. 205Mapping for User-Defined Types. 206Support for svdpi.h Functions. 208DPI Examples Shipped with the Vivado Design Suite. 215Appendix F: Handling Special Cases.216Using Global Reset and 3-State. 216Delta Cycles and Race Conditions. 218Using the ASYNC REG Constraint.219Simulating Configuration Interfaces. 221Disabling Block RAM Collision Checks for Simulation. 224Dumping the Switching Activity Interchange Format File for Power Analysis. 225Skipping Compilation or Simulation. 225UG900 (v2020.1) June 3, 2020Vivado Design Suite User Guide: Logic SimulationSend Feedbackwww.xilinx.com5

Appendix G: Value Rules in Vivado Simulator Tcl Commands. 227String Value Interpretation. 227Vivado Design Suite Simulation Logic. 227Appendix H: Vivado Simulator Mixed Language Support andLanguage Exceptions. 229Using Mixed Language Simulation. 229VHDL Language Support Exceptions. 235Verilog Language Support Exceptions . 236Appendix I: Vivado Simulator Quick Reference Guide. 239Appendix J: Using Xilinx Simulator Interface. 242Preparing the XSI Functions for Dynamic Linking. 242Writing the Test Bench Code. 244Compiling Your C/C Program. 245Preparing the Design Shared Library. 245XSI Function Reference.246Vivado Simulator VHDL Data Format.251Vivado Simulator Verilog Data Format. 254Appendix K: Additional Resources and Legal Notices. 257Xilinx Resources.257Documentation Navigator and Design Hubs. 257References.257Links to Additional Information on Third-Party Simulators.258Training Resources.259Please Read: Important Legal Notices. 259UG900 (v2020.1) June 3, 2020Vivado Design Suite User Guide: Logic SimulationSend Feedbackwww.xilinx.com6

Chapter 1: Logic Simulation OverviewChapter 1Logic Simulation OverviewSimulation is a process of emulating real design behavior in a software environment. Simulationhelps verify the functionality of a design by injecting stimulus and observing the design outputs.This chapter provides an overview of the simulation process, and the simulation options in theVivado Design Suite.The process of simulation includes: Creating test benches, setting up libraries and specifying the simulation settings for Simulation Generating a Netlist (if performing post-synthesis or post-implementation simulation) Running a Simulation using Vivado simulator or third party simulators. See SupportedSimulators for more information on supported simulators.Supported SimulatorsFollowing are the supported simulators in the Vivado Design Suite:Table 1: Supported SimulatorsSimulatorVersionIntegrated with VivadoIntegrated Design EnvironmentVivado Simulator2020.1Integrated with the Vivado integrateddesign environment, where eachsimulation launch appears as aframework of windows within theVivado IDE.Mentor Graphics Questa AdvancedSimulator2019.4YesMentor Graphics ModelSim Simulator2019.4YesCadence Incisive Enterprise Simulator(IES)15.20.079YesSynopsys Verilog Compiler Simulator(VCS)P-2019.06-SP1-1Yes2019.10YesAldec Rivera-PRO SimulatorAldec Active-HDLCadence Xcelium Parallel SimulatorUG900 (v2020.1) June 3, 2020Vivado Design Suite User Guide: Logic Simulation11.1aNo19.09.004YesSend Feedbackwww.xilinx.com7

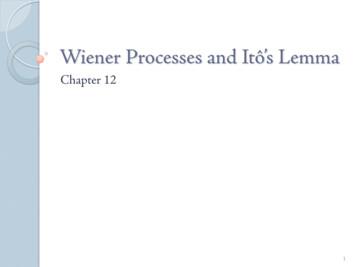

Chapter 1: Logic Simulation OverviewSee the Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973) for thesupported versions of third-party simulators.For more information about the Vivado IDE and the Vivado Design Suite flow, see: Vivado Design Suite User Guide: Using the Vivado IDE (UG893) Vivado Design Suite User Guide: Design Flows Overview (UG892)Simulation FlowSimulation can be applied at several points in the design flow. It is one of the first steps afterdesign entry and one of the last steps after implementation as part of verifying the endfunctionality and performance of the design.Simulation is an iterative process and is typically repeated until both the design functionality andtiming requirements are satisfied.The following figure illustrates the simulation flow for a typical design:UG900 (v2020.1) June 3, 2020Vivado Design Suite User Guide: Logic SimulationSend Feedbackwww.xilinx.com8

Chapter 1: Logic Simulation OverviewFigure 1: Simulation FlowRTL DesignBehavioral Simulation(Verify Design Behaves asIntended)SynthesizePost Synthesis SimulationImplement (Place andRoute)Post ImplementationSimulation(Close to Emulating HW)Debug the DesignX23703-021320Behavioral Simulation at the Register Transfer LevelRegister Transfer Level (RTL) behavioral simulation can include: RTL Code Instantiated UNISIM library components Instantiated UNIMACRO components UNISIM gate-level model (for the Vivado logic analyzer) SECUREIP LibraryRTL-level simulation lets you simulate and verify your design prior to any translation made bysynthesis or implementation tools. You can verify your designs as a module or an entity, a block,a device, or a system.UG900 (v2020.1) June 3, 2020Vivado Design Suite User Guide: Logic SimulationSend Feedbackwww.xilinx.com9

Chapter 1: Logic Simulation OverviewRTL simulation is typically performed to verify code syntax, and to confirm that the code isfunctioning as intended. In this step, the design is primarily described in RTL and consequently,no timing information is required.RTL simulation is not architecture-specific unless the design contains an instantiated devicelibrary component. To support instantiation, Xilinx provides the UNISIM library.When you verify your design at the behavioral RTL you can fix design issues earlier and savedesign cycles.Keeping the initial design creation limited to behavioral code allows for: More readable code Faster and simpler simulation Code portability (the ability to migrate to different device families) Code reuse (the ability to use the same code in future designs)Post-Synthesis SimulationYou can simulate a synthesized netlist to verify that the synthesized design meets the functionalrequirements and behaves as expected. Although it is not typical, you can perform timingsimulation with estimated timing numbers at this simulation point.The functional simulation netlist is a hierarchical, folded netlist expanded to the primitive moduleand entity level; the lowest level of hierarchy consists of primitives and macro primitives.These primitives are contained in the UNISIMS VER library for Verilog, and the UNISIM libraryfor VHDL.Related InformationUNISIM LibraryPost-Implementation SimulationYou can perform functional or timing simulation after implementation. Timing simulation is theclosest emulation to actually downloading a design to a device. It allows you to ensure that theimplemented desig

Simulation is a process of emulating real design behavior in a software environment. Simulation helps verify the functionality of a design by injecting stimulus and observing the design outputs. This chapter provides an overview of the simulation process, and the simulation options in the Vivado Design Suite. The process of simulation includes:

PG300 (v3.0) November 10, 2021 www.xilinx.com DisplayPort 1.4 RX Subsystem v3.0 6. Se n d Fe e d b a c k. Performance and Resource Use web page. Xilinx Design Tools: Release Notes Guide. 70294. 72775. Xilinx Support web page. Xilinx Wiki page. page. Xilinx Design Tools: Rele

Dynamic Logic Dynamic Circuits will be introduced and their performance in terms of power, area, delay, energy and AT2 will be reviewed. We will review the following logic families: Domino logic P-E logic NORA logic 2-phase logic Multiple O/P domino logic Cascode logic

XST User Guide www.xilinx.com 10.1 Xilinx is disclosing this user guide, manual, release note, and/ or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices.

MOSFET Logic Revised: March 22, 2020 ECE2274 Pre-Lab for MOSFET logic LTspice NAND Logic Gate, NOR Logic Gate, and CMOS Inverter Include CRN # and schematics. 1. NMOS NMOSNAND Logic Gate Use Vdd 10Vdc. For the NMOS NAND LOGIC GATE shown below, use the 2N7000 MOSFET LTspice model that has a gate to source voltage Vgs threshold of 2V (Vto 2.0).File Size: 586KB

Digital Logic Fundamentals Unit 1 – Introduction to the Circuit Board 2 LOGIC STATES The output logic state (level) of a gate depends on the logic state of the input(s). There are two logic states: logic 1, or high, and logic 0, or low. The output of some gates can also be in a high-Z (high impedance) state, which is neither a high

categorical and hypothetical syllogism, and modal and inductive logic. It is also associated with the Stoics and their propositional logic, and their work on implication. Syllogistic logic and propositional logic led later to the development of predicate logic (or first order logic, i.e. the foundational logic for mathematics)

AXI Reference Guide www.xilinx.com 5 UG761 (v13.1) March 7, 2011 Chapter 1 Introducing AXI for Xilinx System Development Introduction Xilinx has adopted the Advanced eXtensible Interface (AXI) protocol for Intellectual Property (IP) cores beginning with the Sparta

MS Exemplar Unit English Language Arts Grade 2 Edition 1 Design Overview The MS CCRS Exemplar Units for ELA and mathematics address grade-level specific standards for Pre-Kindergarten-8th grade, as well as for Algebra, English I, and English II. The overall unit plan is described in the first section of the ELA and math units. This section .