DIGITAL ELECTRONICS F.Y.B.Sc.I.T SEM-I

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPDIGITAL ELECTRONICSF.Y.B.Sc.I.TSEM-I4 PageF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPB. Sc (Information Technology)Semester – ICourse Name: Digital Electronics PracticalPeriods per week (1 Period is 50 minutes)CreditsHoursEvaluation System Practical ExaminationInternalList of PracticalCourse Code: USIT1P232Marks2½50---1.Study of Logic gates and their ICs and universal gates:a.Study of AND, OR, NOT, XOR, XNOR, NAND and NOR gatesb.c.d.IC 7400, 7402, 7404, 7408, 7432, 7486, 74266Implement AND, OR, NOT, XOR, XNOR using NAND gates.Implement AND, OR, NOT, XOR, XNOR using NOR gates.2.Implement the given Boolean expressions using minimum number of gates.a.Verifying De Morgan’s laws.b.Implement other given expressions using minimum number of gates.c.Implement other given expressions using minimum number of ICs.3.a.Implement combinational circuits.Design and implement combinational circuit based on the problem given and minimizingusing K-maps.4.Implement code converters.a.Design and implement Binary – to – Gray code converter.b.c.d.Design and implement Gray – to – Binary code converter.Design and implement Binary – to – BCD code converterDesign and implement Binary – to – XS-3 code converter5.Implement Adder and Subtractor Arithmetic circuits.a.Design and implement Half adder and Full adder.b.Design and implement BCD adder.c.Design and implement XS – 3 adder.d.e.f.Design and implement binary subtractor.Design and implement BCD subtractor.Design and implement XS – 3 subtractor.6.Implement Arithmetic circuits.a.Design and implement a 2-bit by 2-bit multiplier.5 PageF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPb.Design and implement a 2-bit comparator.7.a.b.c.d.e.Implement Encode and Decoder and Multiplexer and Demultiplexers.Design and implement 8:3 encoder.Design and implement 3:8 decoder.Design and implement 4:1 multiplexer. Study of IC 74153, 74157Design and implement 1:4 demultiplexer. Study of IC 74139Implement the given expression using IC 74151 8:1 multiplexer.f.Implement the given expression using IC 74138 3:8 decoder.8.a.b.c.d.e.f.Study of flip-flops and counters.Study of IC 7473.Study of IC 7474.Study of IC 7476.Conversion of Flip-flops.Design of 3-bit synchronous counter using 7473 and required gates.Design of 3-bit ripple counter using IC 7473.9.a.b.Study of counter ICs and designing Mod-N counters.Study of IC 7490, 7492, 7493 and designing mod-n counters using these.Designing mod-n counters using IC 7473 and 7400 (NAND gates)10.a.Design of shift registers and shift register counters.Design serial – in serial – out, serial – in parallel – out, parallel – in serial – out, parallel –in parallel – out and bidirectional shift registers using IC 7474.Study of ID 7495.Implementation of digits using seven segment displays.b.c.Books and References:Sr. No. TitleDigital Electronics andLogic Design1.2.Digital Principles andApplicationsAuthor/sN. G. PalanPublisherTechnovaMalvino andLeachTata McGrawHillEditionYear6 PageF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPPRACTICAL-1Study of Logic gates and their ICs anduniversal gates:1.Study of AND, OR, NOT, XOR, XNOR, NAND and NORgates2.IC 7400, 7402, 7404, 7408, 7432, 7486, 742663.Implement AND, OR, NOT, XOR, XNOR using NANDgates.4.Implement AND, OR, NOT, XOR, XNOR using NORgates.7 PageF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPAND GATE:SYMBOL:PIN DIAGRAM:OR GATE:8 PageF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPNOT GATE:SYMBOL:PIN DIAGRAM:X-OR GATE :SYMBOL :PIN DIAGRAM :9 PageF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOP2-INPUT NAND GATE:SYMBOL:PIN DIAGRAM:NOR GATE:10 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOP11 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPIC 7426674266 Quad 2-input Ex-NOR Gate12 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPXOR gate from NAND gates:XOR gate from NOR gates:13 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPPRACTICAL-2Implement the given Boolean expressionsusing minimum number of gates1. Verifying De Morgan’s laws.2. Implement other given expressions using minimum numberof gates. (any expression from Chapter 3, Reference 1)3. Implement other given expressions using minimum numberof ICs. (any expression from Chapter 3, Reference 1)14 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPDe Morgan has suggested two theorems which are extremely useful in Boolean Algebra. The twotheorems are discussed below.Theorem 1 The left hand side LHS of this theorem represents a NAND gate with inputs A and B,whereas the right hand side RHS of the theorem represents an OR gate with invertedinputs. This OR gate is called as Bubbled OR.15 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPTheorem 2The LHS of this theorem represents a NOR gate with inputs A and B, whereas the RHS representsan AND gate with inverted inputs.This AND gate is called as Bubbled AND.16 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPPRACTICAL-3Implement combinational circuitsDesign and implement combinational circuit based on theproblem given and minimizing using K-maps.(any question from Chapter 5, Reference 1)17 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPPRACTICAL-4Implement code converters1. Design and implement Binary – to – Gray codeconverter2. Design and implement Gray – to – Binary codeconverter3. Design and implement Binary – to – BCD code converter4. Design and implement Binary – to – XS-3 code converter18 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPLOGIC DIAGRAM:BINARY TO GRAY CODE CONVERTORK-Map for G3:K-Map for G2:G3 B3K-Map for G1:K-Map for G0:19 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPTRUTH TABLE: Binary inputB3B200000000010101011010101011111111 1111Gray code outputG2G100000101111110101010111101010000 G0011001100110011020 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPLOGIC DIAGRAM:GRAY CODE TO BINARY CONVERTORTRUTH TABLE: Gray Code Binary Code 1111000011110011001100110011010101010101010121 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPK-Map for B3:K-Map for B2:B3 G3K-Map for B1:K-Map for B0:22 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPPIN DIAGRAM FOR IC 7483:23 P a g eF.Y.B.Sc.I.TSEM-1

USHA PRAVIN GANDHI COLLEGE OF MANAGEMENTDIGITAL ELECTRONICS WORKSHOPPRACTICAL-5Implement Adder and Subtractor Arithmetic circuits1. Design and implement half adder and Full adder.2. Design

c. Implement AND, OR, NOT, XOR, XNOR using NAND gates. d. Implement AND, OR, NOT, XOR, XNOR using NOR gates. 2. Implement the given Boolean expressions using minimum number of gates. a. Verifying De Morgan’s laws. b. Implement other given expressions using minimum number of gates. c. Implement other given expressions using minimum number of .

LG Electronics V10 10 LG Electronics V20 10 LG Electronics V30 30 LG Electronics V40 ThinQ Dual SIM 80 LG Electronics V50 ThinQ 160 LG Electronics VELVET 4G 100 LG Electronics VELVET 5G 120 LG Electronics X Powe

E1.2 Digital Electronics I 5.29 Cot 2007 OPEN M F1 M F3 M F2 E1.2 Digital Electronics I 5.30 Cot 2007 The Karnaugh Map with 5 variables E1.2 Digital Electronics I 5.31 Cot 2007 K Map Method Summary Compared to the algebraic method, the K-map process is a more orderly process requiring fewer steps and always producing a minimum expression.

Medical Electronics Lab This Lab facilitates two major skills development: 1. Basic Analog & Digital Electronics 2. Medical Electronics ( Application of electronics in biomedical ) For Basic Electronics skills development the Lab is equipped with Com3 Kits which have electronics trainer boards interfaced with software on PC. This

Analogue Electronics: 24 hours of lectures and tutorials (12 weeks 2 hours/week) Assessment for analogue electronics: Mid-semester test in November, analogue electronics only, 1 hour, 8% of the final mark. Final examination in January, analogue & digital electronics, 2 hours, 50% of the final mark.

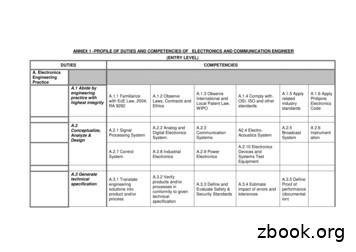

Electronics Code A.2 Conceptualize, Analyze & Design A.2.1 Signal Processing System A.2.2 Analog and Digital Electronics System. A.2.3 Communication Systems A2.4 Electro-Acoustics System A.2.5 Broadcast System A 2.6 Instrument ation A.2.7 Control System. A 2.8 Industrial Electronics A.2.9 Power Electronics A.2.10 Electronics Devices and Systems .

Digital Electronics Digital Electronics Lab Linear Integrated Circuits and Applications . microprocessor –digital computer principles. Division of Electronics and Communication Engineering 3 Unit IV : Measurement . Albert Paul Malvino, Donald P Leach, “Digital Principles a

3 www.understandquran.com ‡m wQwb‡q †bq, †K‡o †bq (ف ط خ) rُ sَ _ْ یَ hLbB َ 9 آُ Zviv P‡j, nv‡U (ي ش م) اْ \َ َ hLb .:اذَإِ AÜKvi nq (م ل ظ) َ9َmْ أَ Zviv uvovj اْ ُ Kَ hw ْ َ Pvb (ء ي ش) ءَ Cﺵَ mewKQy ءٍ ْdﺵَ bِّ آُ kw³kvjx, ¶gZvevb ٌ یْ"ِKَ i“Kz- 3

1 Opto Electronics PG (Opto Electronics & Communication Systems) 2 Fibre Optics PG (Opto Electronics & Communication Systems) 3 Optical Communication Technology PG (Opto Electronics & Communication Systems) 4 Power Electronics B Tech Electrical & Electronics Engg. (CUSAT) 5 DC Machines and Transformers B Tech