HIGH VOLTAGE The MC33363 Is A Monolithic High Voltage .

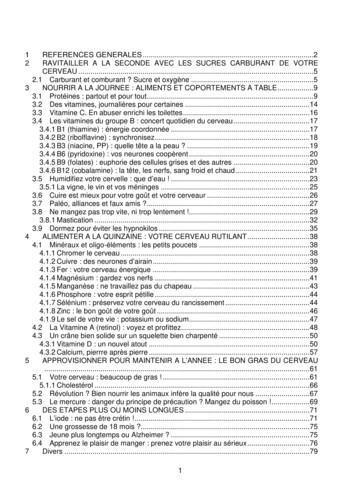

Order this document by MC33363/D The MC33363 is a monolithic high voltage switching regulator that isspecifically designed to operate from a rectified 240 Vac line source. Thisintegrated circuit features an on–chip 700 V/1.0 A SenseFET power switch,450 V active off–line startup FET, duty cycle controlled oscillator, currentlimiting comparator with a programmable threshold and leading edgeblanking, latching pulse width modulator for double pulse suppression, highgain error amplifier, and a trimmed internal bandgap reference. Protectivefeatures include cycle–by–cycle current limiting, input undervoltage lockoutwith hysteresis, output overvoltage protection, and thermal shutdown. Thisdevice is available in a 16–lead dual–in–line and wide body surface mountpackages. On–Chip 700 V, 1.0 A SenseFET Power Switch HIGH VOLTAGEOFF–LINESWITCHING REGULATORSEMICONDUCTORTECHNICAL DATA161Rectified 240 Vac Line Source OperationDW SUFFIXPLASTIC PACKAGECASE 751N(SOP–16L)On–Chip 450 V Active Off–Line Startup FETLatching PWM for Double Pulse SuppressionCycle–By–Cycle Current LimitingInput Undervoltage Lockout with HysteresisOutput Overvoltage Protection ComparatorTrimmed Internal Bandgap ReferenceInternal Thermal Shutdown161P SUFFIXPLASTIC PACKAGECASE 648E(DIP–16)Simplified ApplicationAC InputStartup TCTPIN CONNECTIONSPWM artup Input1VCC3Ipk413512RT611CT710Regulator Output89GndPower SwitchDrainLEBGndOvervoltageProtection InputVoltage FeedbackInputCompensation(Top View)CompensationThermalPower SwitchDrainDC OutputRPWM169EAGnd4, 5, 12, 1310VoltageFeedbackInputORDERING INFORMATIONDeviceOperatingTemperature RangeMC33363DWThis device contains 221 active transistors.MC33363PSOP–16LTJ –25 to 125 C Motorola, Inc. 1998MOTOROLA ANALOG IC DEVICE DATAPackageDIP–16Rev 31

MC33363MAXIMUM ingPower Switch (Pin 16)Drain VoltageDrain CurrentStartup Input Voltage (Pin 1, Note 1)Pin 3 GndPin 3 1000 µF to groundSymbolValueUnitVDSIDS7001.0VAVinV400500Power Supply Voltage (Pin 3)VCC40VInput Voltage RangeVoltage Feedback Input (Pin 10)Compensation (Pin 9)Overvoltage Protection Input (Pin 11)RT (Pin 6)CT (Pin 7)VIR–1.0 to VregVThermal CharacteristicsP Suffix, Dual–In–Line Case 648EThermal Resistance, Junction–to–AirThermal Resistance, Junction–to–Case(Pins 4, 5, 12, 13)DW Suffix, Surface Mount Case 751NThermal Resistance, Junction–to–AirThermal Resistance, Junction–to–Case(Pins 4, 5, 12, 13)Refer to Figures 15 and NO TAG for additionalthermal information.Operating Junction TemperatureStorage TemperatureNOTE: C/WRθJARθJC8015RθJARθJC9515TJ– 25 to 150 CTstg– 55 to 150 CESD data available upon request.ELECTRICAL CHARACTERISTICS (VCC 20 V, RT 10 k, CT 390 pF, CPin 8 1.0 µF, for typical values TJ 25 C,for min/max values TJ is the operating junction temperature range that applies (Note 2), unless otherwise itOutput Voltage (IO 0 mA, TJ 25 C)Vreg5.56.57.5VLine Regulation (VCC 20 V to 40 V)Regline–30500mVLoad Regulation (IO 0 mA to 10 mA)Regload–44200mVVreg5.3–8.0VREGULATOR (Pin 8)Total Output Variation over Line, Load, and TemperatureOSCILLATOR (Pin 7)FrequencyCT 390 pFTJ 25 C (VCC 20 V)TJ Tlow to Thigh (VCC 20 V to 40 V)CT 2.0 nFTJ 25 C (VCC 20 V)TJ Tlow to Thigh (VCC 20 V to 40 V)fOSCkHz260255285–310315605967.5–7576 fOSC/ ��20500nAOpen Loop Voltage Gain (TJ 25 C)AVOL–82–dBGain Bandwidth Product (f 100 kHz, TJ 25 C)GBW–1.0–MHzFrequency Change with Voltage (VCC 20 V to 40 V)ERROR AMPLIFIER (Pins 9, 10)Voltage Feedback Input ThresholdLine Regulation (VCC 20 V to 40 V, TJ 25 C)Input Bias Current (VFB 2.6 V)NOTES: 1. Maximum power dissipation limits must be observed.2. Tested junction temperature range for the MC33363:Tlow –25 CThigh 125 C2MOTOROLA ANALOG IC DEVICE DATA

MC33363ELECTRICAL CHARACTERISTICS (continued) (VCC 20 V, RT 10 k, CT 390 pF, CPin 8 1.0 µF, for typical values TJ 25 C,for min/max values TJ is the operating junction temperature range that applies (Note 2), unless otherwise inTypMaxUnitVOHVOL4.0–5.30.2–0.35Input Threshold VoltageVth2.472.62.73VInput Bias Current (Vin 2.6 ��1732ID(off)–0.250µARise Timetr–50–nsFall ROR AMPLIFIER (Pins 9, 10)Output Voltage SwingHigh State (ISource 100 µA, VFB 2.0 V)Low State (ISink 100 µA, VFB 3.0 V)VOVERVOLTAGE DETECTION (Pin 11)PWM COMPARATOR (Pins 7, 9)Duty CycleMaximum (VFB 0 V)Minimum (VFB 2.7 V)%POWER SWITCH (Pin 16)Drain–Source On–State Resistance (ID 200 mA)TJ 25 CTJ Tlow to ThighΩRDS(on)Drain–Source Off–State Leakage Current (VDS 700 V)OVERCURRENT COMPARATOR (Pin 16)Current Limit Threshold (RT 10 k)STARTUP CONTROL (Pin 1)Peak Startup Current (Vin 400 V)VCC 0 VVCC (Vth(on) – 0.2 V)IstartmAOff–State Leakage Current (Vin 50 V, VCC 20 11.5V––0.253.20.55.0UNDERVOLTAGE LOCKOUT (Pin 3)Startup Threshold (VCC Increasing)Minimum Operating Voltage After Turn–OnTOTAL DEVICE (Pin 3)ICCFigure 1. Oscillator Frequencyversus Timing Resistorf OSC , OSCILLATOR FREQUENCY (Hz)1.0 MCT 100 pFVCC 20 VTA 25 C500 k C 200 pFT200 k CT 500 pF100 k CT 1.0 nFC 2.0 nF50 k TC 5.0 nF20 k TCT 10 nF10 k7.010152030RT, TIMING RESISTOR (kΩ)MOTOROLA ANALOG IC DEVICE DATA5070I PK, POWER SWITCH PEAK DRAIN CURRENT (A)Power Supply CurrentStartup (VCC 10 V, Pin 1 Open)OperatingmAFigure 2. Power Switch Peak Drain Currentversus Timing Resistor1.0VCC 20 VCT 1.0 µFTA 25 C0.80.60.40.2Inductor supply voltage and inductance value areadjusted so that Ipk turn–off is achieved at 5.0 µs.0.17.010152030407050RT, TIMING RESISTOR (kΩ)3

MC33363Figure 4. Maximum Output Duty Cycleversus Timing Resistor RatioDmax, MAXIMUM OUTPUT DUTY CYCLE (%)Figure 3. Oscillator Charge/DischargeCurrent versus Timing Resistor0.50.30.20.150.1101520305070605040RC/RT RatioCharge ResistorPin 6 to Vreg301.02.03.05.07.0Figure 5. Error Amp Open Loop Gain andPhase versus FrequencyFigure 6. Error Amp Output SaturationVoltage versus Load CurrentVCC 20 VVO 1.0 to 4.0 VRL 5.0 MΩCL 2.0 pFTA 25 C80Gain6003060Phase40902012001501001.0 k10 k100 k1.0 M18010 MSource Saturation(Load to Ground)–1.0Vref– 2.02.0Sink Saturation(Load to Vref)1.0VCC 20 VTA 25 CGnd000.20.40.60.8IO, OUTPUT LOAD CURRENT (mA)Figure 7. Error Amplifier Small SignalTransient ResponseFigure 8. Error Amplifier Large SignalTransient ResponseVCC 20 VAV –1.0CL 10 pFTA 25 C1.0VCC 20 VAV –1.0CL 10 pFTA 25 C0.5 V/DIV3.00 V20 mV/DIV1.75 V100f, FREQUENCY (Hz)1.80 V1.75 V0.50 V1.70 V1.0 µs/DIV4VCC 20 VCT 2.0 nFTA 25 CRD/RT RatioDischarge ResistorPin 6 to GndTIMING RESISTOR RATIO100– 201070RT, TIMING RESISTOR (kΩ)Vsat , OUTPUT SATURATION VOLTAGE (V)0.087.0A VOL, OPEN LOOP VOLTAGE GAIN (dB)VCC 20 VTA 25 Cθ, EXCESS PHASE (DEGREES)I chg /I dscg , OSCILLATORCHARGE/DISCHARGE CURRENT (mA)0.81.0 µs/DIVMOTOROLA ANALOG IC DEVICE DATA

Figure 10. Peak Startup Currentversus Power Supply VoltageFigure 9. Regulator Output VoltageChange versus Source Current200– 20– 40– 60– 80VPin 1 400 VTA 25 CI pk , PEAK STARTUP CURRENT (mA)VCC 20 VRT 10 kCPIN 8 1.0 µFTA 25 C10Pulse tested with an on–time of 20 µs to 300 µsat 1.0% duty cycle. The on–time is adjusted atPin 1 for a maximum peak current out of Pin 3.04.008.01216204.06.08.01012Figure 11. Power Switch Drain–SourceOn–Resistance versus TemperatureFigure 12. Power SwitchDrain–Source Capacitance versus VoltageID 200 mA24168.0Pulse tested at 5.0 ms with 1.0% duty cycleso that TJ is as close to TA as possible.–250255075100125VCC 20 VTA 25 C120804001.0150COSS measured at 1.0 MHz with 50 mVpp.101001000VDS, DRAIN–SOURCE VOLTAGE (V)Figure 13. Supply Current versus Supply VoltageFigure 14. DW and P Suffix TransientThermal Resistance1002.4Rθ JA , THERMAL RESISTANCEJUNCTION–TO–AIR ( C/W)CT 390 pFCT 2.0 nF1.6RT 10 kPin 1 OpenPin 4, 5, 10, 11,12, 13 GndTA 25 C0.8014160TA, AMBIENT TEMPERATURE ( C)3.2I CC, SUPPLY CURRENT (mA)2.0VCC, POWER SUPPLY VOLTAGE (V)320–500Ireg, REGULATOR SOURCE CURRENT (mA)COSS, DRAIN–SOURCE CAPACITANCE (pF)R DS(on), DRAIN–SOURCE ON–RESISTANCE (Ω ) V reg, REGULATOR VOLTAGE CHANGE (mV)MC3336301020VCC, SUPPLY VOLTAGE (V)MOTOROLA ANALOG IC DEVICE DATA3040L 12.7 mm of 2.0 oz.copper. Refer to Figures15 and NO TAG.101.00.010.11.010100t, TIME (s)5

Printed circuit board heatsink example702.0 ozCopperL60L3.0 mmGraphs represent symmetrical ÏÏÏÏÏÏÏÏÏ1005.0Printed circuit board heatsink example80LRθJA604.02.0 ozCopperL3.0 mmGraphs represent symmetrical layout3.0402.0PD(max) for TA 70 C200010L, LENGTH OF COPPER (mm)201.03040050P D , MAXIMUM POWER DISSIPATION (W)Rθ JA , THERMAL RESISTANCEJUNCTION–TO–AIR ( C/W)PD(max) for TA 50 CFigure 16. P Suffix (DIP–16) Thermal Resistance andMaximum Power Dissipation versus P.C.B. Copper LengthR θ JA, THERMAL RESISTANCEJUNCTION–TO–AIR ( C/W)2.8100PD, MAXIMUM POWER DISSIPATION (W)Figure 15. DW Suffix (SOP–16L) Thermal Resistance andMaximum Power Dissipation versus P.C.B. Copper LengthL, LENGTH OF COPPER ÁÁPIN FUNCTION DESCRIPTIONPinDescription1Startup InputThis pin connects directly to the rectified ac line voltage source. Internally Pin 1 is tied to the drainof a high voltage startup MOSFET. During startup, the MOSFET supplies internal bias, and chargesan external capacitor that connects from the VCC pin to ground.2–This pin has been omitted for increased spacing between the rectified ac line voltage on Pin 1 andthe VCC potential on Pin 3.3VCCThis is the positive supply voltage input. During startup, power is supplied to this input from Pin 1.When VCC reaches the UVLO upper threshold, the startup MOSFET turns off and power is suppliedfrom an auxiliary transformer winding.GroundThese pins are the control circuit grounds. They are part of the IC lead frame and provide a thermalpath from the die to the printed circuit board.6RTResistor RT connects from this pin to ground. The value selected will program the Current LimitComparator threshold and affect the Oscillator frequency.7CTCapacitor CT connects from this pin to ground. The value selected, in conjunction with resistor RT,programs the Oscillator frequency.8Regulator OutputThis 6.5 V output is available for biasing external circuitry. It requires an external bypass capacitorof at least 1.0 µF for stability.9CompensationThis pin is the Error Amplifier output and is made available for loop compensation. It can be used asan input to directly control the PWM Comparator.10Voltage FeedbackInputThis is the inverting input of the Error Amplifier. It has a 2.6 V threshold and normally connectsthrough a resistor divider to the converter output, or to a voltage that represents the converteroutput.11OvervoltageProtection InputThis input provides runaway output voltage protection due to an external component or connectionfailure in the control loop feedback signal path. It has a 2.6 V threshold and normally connectsthrough a resistor divider to the converter output, or to a voltage that represents the converteroutput.–These pins have been omitted for increased spacing between the high voltages present on thePower Switch Drain, and the ground potential on Pins 12 and 13.Power SwitchDrainThis pin is designed to directly drive the converter transformer and is capable of switching amaximum of 700 V and 1.0 A.4, 5, 12, 1314, 15166FunctionMOTOROLA ANALOG IC DEVICE DATA

MC33363Figure 17. Representative Block DiagramAC InputStartup InputStartupControlCurrentMirrorRegulator Output6.5 V8Band GapRegulatorIVCCCT3UVLO2.25 I4IOVP112.6 VOscillator7DC OutputOvervoltageProtectionInput14.5 V/9.5 V6RT116PWM LatchPower SwitchDrainDriverSQRPWMComparatorLeading EdgeBlanking9.0ThermalShutdownCurrent LimitComparatorCompensation450270 µAGnd9ErrorAmplifier2.6 V10VoltageFeedback Input4, 5, 12, 13Figure 18. Timing Diagram2.6 VCapacitor CT0.6 VCompensationOscillator OutputPWMComparatorOutputPWM LatchQ OutputCurrent LimitPropagationDelayPower SwitchGate DriveCurrentLimitThresholdLeading EdgeBlanking Input(Power SwitchDrain Current)Normal PWM Operating RangeMOTOROLA ANALOG IC DEVICE DATAOutput Overload7

MC33363OPERATING DESCRIPTIONIntroductionThe MC33363 represents a new higher level of integrationby providing all the active high voltage power, control, andprotection circuitry required for implementation of a flyback orforward converter on a single monolithic chip. This device isdesigned for direct operation from a rectified 240 Vac linesource and requires a minimum number of externalcomponents to implement a complete converter. Adescription of each of the functional blocks is given below,and the representative block and timing diagrams are shownin Figures 17 and 18.The formula for the charge/discharge current along withthe oscillator frequency are given below. The frequencyformula is a first order approximation and is accurate for CTvalues greater than 500 pF. For smaller values of CT, refer toFigure 1. Note that resistor RT also programs the CurrentLimit Comparator threshold.Oscillator and Current MirrorThe oscillator frequency is controlled by the valuesselected for the timing components RT and CT. Resistor RTprograms the oscillator charge/discharge current via theCurrent Mirror 4 I output, Figure 3. Capacitor CT is chargedand discharged by an equal magnitude internal currentsource and sink. This generates a symmetrical 50 percentduty cycle waveform at Pin 7, with a peak and valleythreshold of 2.6 V and 0.6 V respectively. During thedischarge of CT, the oscillator generates an internal blankingpulse that holds the inverting input of the AND gate Driverhigh. This causes the Power Switch gate drive to be held in alow state, thus producing a well controlled amount of outputdeadtime. The amount of deadtime is relatively constant withrespect to the oscillator frequency when operating below1.0 MHz. The maximum Power Switch duty cycle at Pin 16can be modified from the internal 50% limit by providing anadditional charge or discharge current path to CT, Figure 19.In order to increase the maximum duty cycle, a dischargecurrent resistor RD is connected from Pin 7 to ground. Todecrease the maximum duty cycle, a charge current resistorRC is connected from Pin 7 to the Regulator Output. Figure 4shows an obtainable range of maximum output duty cycleversus the ratio of either RC or RD with respect to RT.PWM Comparator and LatchThe pulse width modulator consists of a comparator withthe oscillator ramp voltage applied to the non–inverting input,while the error amplifier output is applied into the invertinginput. The Oscillator applies a set pulse to the PWM Latchwhile CT is discharging, and upon reaching the valleyvoltage, Power Switch conduction is initiated. When CTcharges to a voltage that exceeds the error amplifier output,the PWM Latch is reset, thus terminating Power Switchconduction for the duration of the oscillator ramp–up period.This PWM Comparator/Latch combination prevents multipleoutput pulses during a given oscillator clock cycle. The timingdiagram shown in Figure 18 illustrates the Power Switch dutycycle behavior versus the Compensation voltage.Figure 19. Maximum Duty Cycle ModificationCurrentMirrorRegulator Output1.082.25 mparator8BlankingPulseI 5.4RchgńdscgTf[Ińchg dscg4CTCurrent Limit Comparator and Power SwitchThe MC33363 uses cycle–by–cycle current limiting as ameans of protecting the output switch transistor fromoverstress. Each on–cycle is treated as a separate situation.Current limiting is implemented by monitoring the outputswitch current buildup during conduction, and upon sensingan overcurrent condition, immediately turning off the swi

IDS 700 1.0 V A Pin 3 Gnd Pin 3 1000 µF to ground Vin 400 500 Power Supply Voltage (Pin 3) VCC 40 V T Input Voltage Range Voltage Feedback Input (Pin 10) Compensation (Pin 9) Overvoltage Protection Input (Pin 11) R (Pin 6) CT (Pin 7) VIR –1.0 to Vreg V θ Thermal Characteristics P Suff

May 02, 2018 · D. Program Evaluation ͟The organization has provided a description of the framework for how each program will be evaluated. The framework should include all the elements below: ͟The evaluation methods are cost-effective for the organization ͟Quantitative and qualitative data is being collected (at Basics tier, data collection must have begun)

Silat is a combative art of self-defense and survival rooted from Matay archipelago. It was traced at thé early of Langkasuka Kingdom (2nd century CE) till thé reign of Melaka (Malaysia) Sultanate era (13th century). Silat has now evolved to become part of social culture and tradition with thé appearance of a fine physical and spiritual .

On an exceptional basis, Member States may request UNESCO to provide thé candidates with access to thé platform so they can complète thé form by themselves. Thèse requests must be addressed to esd rize unesco. or by 15 A ril 2021 UNESCO will provide thé nomineewith accessto thé platform via their émail address.

̶The leading indicator of employee engagement is based on the quality of the relationship between employee and supervisor Empower your managers! ̶Help them understand the impact on the organization ̶Share important changes, plan options, tasks, and deadlines ̶Provide key messages and talking points ̶Prepare them to answer employee questions

Dr. Sunita Bharatwal** Dr. Pawan Garga*** Abstract Customer satisfaction is derived from thè functionalities and values, a product or Service can provide. The current study aims to segregate thè dimensions of ordine Service quality and gather insights on its impact on web shopping. The trends of purchases have

Chính Văn.- Còn đức Thế tôn thì tuệ giác cực kỳ trong sạch 8: hiện hành bất nhị 9, đạt đến vô tướng 10, đứng vào chỗ đứng của các đức Thế tôn 11, thể hiện tính bình đẳng của các Ngài, đến chỗ không còn chướng ngại 12, giáo pháp không thể khuynh đảo, tâm thức không bị cản trở, cái được

Le genou de Lucy. Odile Jacob. 1999. Coppens Y. Pré-textes. L’homme préhistorique en morceaux. Eds Odile Jacob. 2011. Costentin J., Delaveau P. Café, thé, chocolat, les bons effets sur le cerveau et pour le corps. Editions Odile Jacob. 2010. Crawford M., Marsh D. The driving force : food in human evolution and the future.

The Zipwhip Messaging API supports both single -user and multi-user authentication. If you use single-user authentication, then all users are Administrators (Admin). There is a single tier of users. If you use multi-user authentication, then at least one user is the Administrator and all other users are Operators. There are two tiers of users .