Evolution Of Processor Architecture In Mobile Phones

International Journal of Computer Applications (0975 – 8887)Volume 90 – No 4, March 2014Evolution of Processor Architecture in Mobile PhonesMahendra Pratap SinghResearch Scholar,Department of Computer Science, MohanlalSukhadia University, Udaipur, IndiaABSTRACTMobile phone has become a vital component of our daily life.Technological advancements have resulted in significantchanges in the processor architecture of mobile phones;transforming the typical mobile phones of 1990’s to modernsmart phones. The design and deployment of mobileprocessors over the years is largely affected byCommunication, performance, and low-power operation. Thetransition from analog to digital telephony has resulted inmobile devices delivering a wide range of data services. Tosupport these services, processor architecture has now becomemuch more complex. Mobile processors are growing rapidlywith each passing generation. The goal of this paper is toreview various processor architectures for mobile phones.KeywordsProcessor architecture, DSP, VLIW, SoC, ARM processors1. INTRODUCTIONSmartphone hardware mainly consists of applicationprocessors (System-on-a-Chip), RAM (mobile SDRAM/mobile DDR), DSP, CPU (ARM processor), etc. Accordingto Farinaz et al [1], Processors that are used for mobile phonesare subject to design metrics that emphasize cost, time-tomarket, and low power. Because of the constrained resourcesof power and cost, and the real-time computationrequirements, the processors for use in mobile applicationspossess a number of distinct characteristics such as limitedprogrammability.Processor architecture of mobile devices delivering dataservices must provide support for much more complex userinterface, dynamic operating environments, and support foradditional services. To provide for these additionalrequirements, advanced architectures may include multipleDSP’s or hardware coprocessors.2. MOBILE PROCESSORARCHITECTURE TRENDS2.1 Traditional DSP (Digital SignalProcessor) ArchitecturesManoj Kumar Jain, Ph. DAssociate Professor, Computer ScienceMohanlal Sukhadia UniversityUdaipur, IndiaThere have been two distinct approaches for implementationof cellular handsets. One approach emphasizes programmableDSP’s, while the other approach utilizes ASIC (Applicationspecific integrated circuit) techniques [6].DSP is a specialized microprocessor used for mobile phones.Historically DSP’s were designed around single stand-aloneintegrated circuits (ICs). Embedded DSP’s are now widelyadopted for VLSI designs. Programmable DSP’s are dominantin wireless handset market for digital cellular telephony.First generation of mobile communications i.e. 1G systemsused analog transmission with the limitations of requiringmore power for transmission and allowing limited users[2].Global System for Mobile Communications (GSM) standardevolved after first generation of mobile communication foranalog cellular networks. DSP processors form one of themost important classes of mobile embedded processors insecond generation i.e. 2G systems.DSP architectures are preferred over ASIC due to shorterproduct life cycle and they are extensively used in GSMmobiles. Programmable DSP’s provide a cost-effective andflexible architecture for cellular telephones. AT&T in 1979introduced first DSP, and subsequently Texas Instrumentscame up with other DSP’s.Traditionally, DSP used Harvard architecture whichphysically separates storage and signal pathway forinstructions and data [2]. This is in contrast with VonNeumann Architecture, where data and instructions are storedin the same memory. As shown in Figure 1, it requires datamemory and instruction memory to execute instructions. Ithas separate data and instruction buses allowing simultaneoustransmission. Subsequently, the output of multiplication unitconnects to an adder, thereby adding and saving all partialresults for further processing.This architecture results in fewer cycles for executing aparticular function as it enables high memory bandwidth andmultiple operand operations. Multiply-accumulate (MAC)instructions are commonly associated with DSP architectures.34

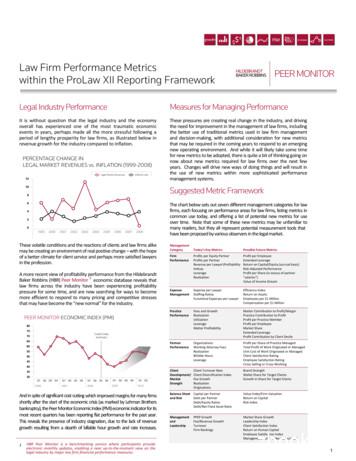

International Journal of Computer Applications (0975 – 8887)Volume 90 – No 4, March 2014DATAMEMORYCONTROL& LOUTSTATUSCLOCKFigure 1: Traditional DSP Architecture (Harvard Architecture)2.2 Modern DSP ArchitecturesApart from traditional architectures, some modern DSParchitectures have evolved for mobile devices. TMS320C55 isa modern DSP architecture which implements Harvardarchitecture utilizing one and three read buses for code anddata, respectively [2]. With TMS320C55 DSP architecture,features like programmable idle modes and automatic powersaving were incorporated for better processor utilization at topspeeds.TMS320C62XX is an example of VLIW (Very longinstruction word) DSP processor. VLIW architecture in DSPprovides a compiler based programmer friendly environment.These VLIW processors follow explicitly parallel instructioncomputing (EPIC) architectures.The TigerSHARK DSP architecture has a series of advancedfeatures like the use of “short vectors” to process informationusing SIMD (single instruction multiple memory) architecture[2].DSPs have become common in mobile devices because theyprovide real-time operation at low power costs. Future mobiledevices have to be aligned to integrate more s.Advancements in DSP lead to higher clock frequencies aswell as a reduced power consumption per MIPS for mobilephones [3].One way of customization is parallelism in superscalardesigns, which is widely implemented for future mobileprocessors. VLIW and SIMD architectures in modern cellulardevices are becoming more and more popular; because theyallow reducing the frequency and voltage of the CPU chipswithout losing performance. Modern DSPs can be moreeffective if they are able to support parallel processing.In modern DSP architectures, computational power hasgreatly improved due to advancements in chip fabrication. Asshown in Table 1 below, the same DSP chip was providingapproximately 5 GIPS (Giga Instructions per Second) in 2000,in contrast to 5 MIPS in 1980 and it has grown to 50 GIPS inthe year 2010. Considering other factors also, theadvancements in DSP integration is significant.Table 1: DSP Integration over the YearsParameter1980199020002010Die Size 40500050000MHz2080100010000RAM (bytes)2562000320001000000Price ansistors50000500000550millionmillionWafer Size361212(inches)Source: Past and Projected Evolution of DSP [Gene 2000)A number of FPGA (Field-programmable gate array)architectures have been specifically designed for DSP toeffectively utilize VLSI resources. VLIW compilers areextensively used in DSP architectures to support instructionlevel parallelism [. The trend in modern DSP architectures isto develop fault-tolerant and reliable DSP systems. DSPsystems are reconfigured keeping in mind a number of designgoals like performance, power, reliability, cost, anddevelopment time. Modern DSP systems are implementedbased on reconfigurable DSP architectures.In modern DSP’s, architecture can be extended by duplicatingthe processor cores. Enhanced DSP’s utilizes SIMDoperations, while multiple-issue DSP’s may implement eitherVLIW or superscalar architectures.2.3 System on Chip (SoC) basedarchitecturesMobile device processor architecture became simple withSOC designs. Real time responsiveness in mobile devices canbe managed by using an enhanced DSP hybrid chip. Loweringthe voltage of the chip enables low power operation in mobiledevices.35

International Journal of Computer Applications (0975 – 8887)Volume 90 – No 4, March 2014Matthias et al [5] proposed a new scalable DSP architecturefor SoC domains. In SoC based designs, system tasks can bemanaged by integrating microcontrollers, dedicated ASIC’s,or DSP’s in a single chip as shown in Figure 2 below:30Figure 2: Traditional DSP Architecture (HarvardArchitecture)Direct Memory AccessNICAUDI020151050StorageARM CPUDigital SignalProcessor (DSP)Operations per CycleMultimedia Decoders/EncodersMemorySoC Chip25USBVIDEOHighly integrated SoC’s leveraging multicore technology hasemerged for higher performance and low power designs. Lowpower operation often limits the architectural choices. Highthroughput of VLIW architectures in mobile devices requiresa fast memory system like cache memories.To speed up the operation of mobile devices, instruction secustomizations have been done by many companies.ARMLtd. has done extensive instruction set customization byencoding most used instructions in 16-bit, so as to supportmore read-write operations.The effect of instruction set customization on performanceand memory utilization can be understood from Figure 3. Aswe customize instruction set from 32-bit data types to 8-bittypes, we are able to effectively improve memory utilizationand the overall performance.Martin at el [13] proposed reconfigurable processorarchitecture for mobile phones. Dynamically ConfigurableSystem on Chip (CSoC) architecture has been optimized formobile communications. CSoC’s are customized for a specificapplication and its architecture consists of processor core,memory, ASIC cores, and on-chip reconfigurable hardwareunits.Most of the smart phones today are single or dual-core SoC’s.For most of the mobile applications, faster dual-core CPUprovides better performance than quad-core SoC’s. FutureSoC’s for mobile will become more sophisticated improvingthe overall performance.Floating32-bit16-bit8-bitPerformance and Memory UtilizationFigure 3: Effect of Instruction Set Customization onperformance and memory utilization2.4 ARM Processors for MobilesARM based processors are the most widely used in modernSmart phones. ARM is a32-bit instruction set architecturebased on RISC architecture [10]. ARM processors areparticularly used in Smart phones because of its low powerconsumption and great performance.ARM holdings provide chip design and instruction setcustomization licenses to third party vendors like Apple,Qualcomm etc. who design their own products based on theprovided architecture.Various ARM architectures used in Smartphone are ARMv5utilized in low-end devices, and ARMv6, ARMv7 utilized inrecent high performance devices. ARMv7 includes ahardware floating-point unit (FPU) providing improved speed.The 32-bit ARM architecture, such as ARMv7-A, is the mostextensively used architecture in mobile devices.ARM architecture is the main hardware architecture for mostof the operating systems of mobile devices such as iOS,Android, Windows Phone, Windows RT, Bada, BlackberryOS/Blackberry10, MeeGo, FirefoxOS, Tizen, UbuntuTouch, Sailfish and Igelle OS.3. COMPARATIVE STUDY OFCONTEMPORARY MOBILE PHONEPROCESSORSARM Cortex, Snapdragon, Nvidia Tegra are among the mostwidely used mobile processors.3.1 ARM Cortex ProcessorsARM Cortex processors cores are categorized into thefollowing variants: Cortex-A Processors (ARM Application Processors) Cortex-R Processors (ARM Embedded Real-timeProcessors) Cortex-M Processors (ARM Embedded Processors)36

International Journal of Computer Applications (0975 – 8887)Volume 90 – No 4, March 2014 SecureCore Processors (ARM Secure Processors)As an example, consider the architecture of ARM Cortex-A8depicted in Figure 4. This architecture is based on NEONSIMD media and signal processing technology for providingaudio, video, and 3D graphics to mobile applications.Instruction ser architecture of ARM Cortex-A8 implementsThumb-2 instruction set encoding consisting of 16-bit longinstructions which require less external memory. AMBA(Advanced Microcontroller Bus Architecture) bus interfacesupports input and output data buses that are either 64 or 128bit wider. It performs L2 cache fills and non-cacheableaccesses for both instructions and data.Figure 4: ARM Cortex-A8 Architectureexpected to offer 25% less power consumption and will allowup to 30% faster clock speeds.Mobile computing is gearing up for a drastic change this yearwith the advent of 64-bit ARM based processors which areexpected to provide up to 50% performance improvementover existing 32-bit ARM processors. ARM’s new CortexA50 processor series based on the ARMv8 architectureincludes the Cortex-A53 and Cortex-A57 processors. TheCortex-A57 is a performance-oriented applications processor,while the Cortex-A53 is a power-efficient applicationprocessor.In the near future, Android 5.0 will efficiently utilize the newARMv8 64-bit architecture. Apart from the proposed 64-bitarchitectures, upcoming mobile phones will be equipped with4 GB of RAM to support increasing complexity of 3D gameson Android.3.2 Qualcomm Snapdragon ProcessorsSnapdragon is a family of mobile system on a chip (SoC)processor architecture provided by Qualcomm. Scorpion, theoriginal snapdragon CPU had many features similar to ARMCortex-A8 core based on ARMv7 instruction set, but with anadded advantage of higher performance utilizing SIMDoperations.Qualcomm Snapdragon Soc’s are build around Kraitprocessor architecture, shown in Figure 5. It integrates LTE(Long Term Evolution) modem to support seamlessconnectivity across 2G, 3G and 4G LTE networks. Thisarchitecture supports a wider front-end, with the ability tofetch and decode three instructions per clock. Adreno GPU inthis architecture delivers improved advanced graphicsperformance. With Hexagon DSP’s, this architecture provideslow power operation for a variety of multimedia applicationslike enhanced audio/video.A single core ARM Cortex A8 processor with 1.4 GHz clockspeed was considered reasonably enough till 2011. In the year2014, ARM processors clocked at 3 GHz will become areality. These upcoming 20 nm manufactured processors areFigure 5: Qualcomm Snapdragon Processor ArchitectureQualcomm was one of the first to introduce a 28nm processorin 2012 with its Snapdragon S4 series processor. GPU andoverall architecture are refined inside the Snapdragon 600 and800, but they are still utilizing 28nm processors.In the year 2013, Qualcomm Snapdragon 800 processor withKrait 400 CPU cores providing 2.3 GHz clock speedoutperformed all other processors in the mobile segment.37

International Journal of Computer Applications (0975 – 8887)Volume 90 – No 4, March 2014As shown in figure 6 below, Snapdragon 800 processorconsists of 28nm HPm quad core Krait 400 CPU for highperformance, Adreno 330 GPU for improved graphicsperformance, Hexagon DSP for low power operation, andGobi True 4G LTE modem for connectivity.advanced imaging.3.3 Nvidia Tegra ProcessorsTegra is a SoC series for mobile devices developed by Nvidia.It integrates ARM architecture CPU, graphics processing unit(GPU), memory controllers, etc. on a single package. Itenables high performance and low power consumption foraudio/ video applications.Figure 6: Qualcomm Snapdragon 800 ProcessorArchitectureNvidia Tegra 4 processor is a quad-core Soc with increasedGPU cores, faster clock cycles, and improved efficiency. TheGPU architecture of Tegra 4 is shown in Figure 6. Verticesare processed by six VPE (vertex processing engine) units.Next, vertices are cached by IDX unit. Vertices are thenpassed to raster engine, which produces pixel fragments.Early-Z unit tests pixel fragments for Z-depth and passes onlyvisible pixels. Early-Z processing in Tegra 4 GPU architectureresults in improved performance and power savings. GPUincludes four pixel fragment shader pipes which implementsVLIW architecture. Each pixel shader unit also contains atexture filtering unit, with their own L1 and L2 cache.Krait CPUMultimediaAdreno CPUHexagon CPUCameraConnectivityDisplay / LCDAccording to an analysis of upcoming ARM processors, itwas revealed that Nvidia’s Tegra 4 SoC beats the bestQualcomm Snapdragon processor in terms of performance.Though Nvidia have designed a technically faster SoC, butwhen it comes to power efficiency Qualcomm Snapdragonprocessors have an edge.NavigationSnapdragon 800 processors are designed to enable incrediblyfast apps and web browsing, visually stunning sscommunications virtually anytime, anywhere, and outstandingbattery life for premium smart phones.Nvidia has recently launched next generation mobileprocessor, Tegra K1. It is a mobile processor with 192graphics cores for mobile gaming applications. Nvidia K1 waslaunched with a support for two versions: traditional 32-bit“4 1” ARM cores like Tegra 4, and dual core 64-bit version.It is said that Tegra K1 is even more powerful than either theXbox 360 or the PlayStation 3Snapdragon 800 processor provides seamless connectedcomputing and a rich mobile experience with advancedfeatures like Ultra HD video, multichannel HD audio andVertexVertexVertexVertexVertexVertexIDX / Clip / SetupRaster / Early ZTexL2L132b FBTexTexL1MemoryTexL1L132b FBFigure 7: Nvidia Tegra 4 GPU Architecture38

International Journal of Computer Applications (0975 – 8887)Volume 90 – No 4, March 20144. CONCLUSIONDifferent vendors are working towards the development ofmore power efficient mobile processor architectures bylooking at the future of mobile computing. All the modernmobile processors are basically ARM-based, designated withfancy names by different cellular companies.With newer versions of mobile CPU’s we will have morepowerful Smartphone with new GPU cores, memoryinterfaces, and many more advanced features. Future mobileSoC’s will explore next generation processor architecture toimprove the device performance. Mobile processing unitmanufacturers are working hard to develop powerful cellphone devices.To support next-generation data-centric mobile devices,processor architecture has to be designed considering newapproaches. Still, the development in mobile processors isdriven by factors such as low-power consumption, userinterface performance, time to market, etc.5. REFERENCES[1] Farinaz Kaushanfar, Vandana Prabhu, Miodrag Potkonjak,Jan M. Rabaey: “Processors for Mobile Applications”.[2] Dr. Margarita Esponda: “Trends in Hardware Architecturefor Mobile Devices”.[3] Shiv Chaturvedi: “The role of digital signal processors(DSP) for 3G mobile communication systems”,International Journal on Emerging Technologies 1(1):23-26(2010).[4] “TMS320C62xx CPU and Instruction Set ReferenceGuide”: Texas Instruments.IJCATM : www.ijcaonline.org[5] Matthias H. Weiss, Frank Engel, and Gerhard P. Fettweis:“A new Scalable DSP Architecture for System on Chip(SOC) Domains”, IEEE International Conference onAcoustics, Speech, and Signal Processing.[6] Alan Gatherer, Trudy Stetzler, Mike McMahan, and ectures for Mobile Communications: Past, Present,and Future”.[7] Ravi Managuli, Yongmin Kim: “VLIW ProcessorArchitectures and Algorithm Mappings for DSPApplications”.[8] VLIW Architectures for DSP: “Berkeley DesignTechnology, Inc.”[9] Andrew Fallows and Patrick Ganson: “SmartphoneHardware Architecture”.[10] Leonid Ryzhyk: “The ARM Architecture”.[11] “ARM Processor Architecture”, SOC Consortium.[12] Georgescu, M.D: “Evolution of Mobile Processors”,Communications, Computers and signal Processing,2003. PACRIM. 2003 IEEE Pacific Rim Conference.[13] Martin Vorbach, Gurgen Becker: “Reconfigurableprocessor architectures for mobile phones”, Parallel andDistributed Processing Symposium, 2003. Proceedings.International.[14] Russel Tessier and Wayne Burleson: “ReconfigurableComputing for Digital Signal Processing”, Journal ofVLSI Signal Processing 28, 7–27, 2001.39

Mobile computing is gearing up for a drastic change this year with the advent of 64-bit ARM based processors which are expected to provide up to 50% performance improvement over existing 32-bit ARM processors. ARM's new Cortex-A50 processor series based on the ARMv8 architecture includes the Cortex-A53 and Cortex-A57 processors. .

Alfa Romeo 145 old Processor new Processor 2004 146 old Processor By new Processor DIGA-Soft.de 147 Eeprom 147 NEC-Processor 156 before 2002 Cluster-Plug since 2002 Cluster-Plug 159 Eeprom 166 Processor Model 2002 Eeprom Spider Processor GT Eeprom GTV Processor All JTD (Diesel)

Architecture vs Micro-architecture Architecture: ! Parts of processor design needed to write programs in assembly ! What is visible to s/w E.g Number of registers Micro-Architecture: ! Detail of how architecture is implemented E.g Core frequency of the processor Aside: Processor Speed: Intel Core i7: 1.8 GHz

processor appears as a single processor running a single C program. This is very different from some other parallel processing models where the programmer has to explicitly program multiple independent processor cores, or can only access the processor via function calls or some other indirect mechanism. The processor executes a single instruction

- The annoying post office dispatch of the equipment is void. . Alfa Romeo 145 old Processor new Processor . 147 NEC-Processor 156 before 2002 Cluster-Plug since 2002 Cluster-Plug 159 Eeprom 166 Processor Model 2002 Eeprom Spider Processor GT Eeprom GTV Processor All JTD (Diesel) Motor-Control Unit .

3050 SFF Intel i 5-7 00. Puertos y ranuras: factor de forma pequeño 1. Botón de encendido 2. . Small Form Factor Height: 289.6 mm Weight (Approximate): 5.14 kg Width: 94 mm Processor & Chipset Processor Generation: 7th Gen Processor Manufacturer: Intel Processor Model: i5-7500 . Processor Speed: 3.40 GHz Processor Type: Core i5 Software .

ThinkPad X1 Titanium Yoga Gen 1 PSREF Product Specifications Reference ThinkPad X1 Titanium Yoga Gen 1 - December 08 2022 1 of 8. PERFORMANCE Processor Processor Family 11th Generation Intel Core i5 / i7 Processor Processor** Processor Name Cores Threads Base Frequency Max Frequency Cache Memory Support Processor Graphics

What is Computer Architecture? “Computer Architecture is the science and art of selecting and interconnecting hardware components to create computers that meet functional, performance and cost goals.” - WWW Computer Architecture Page An analogy to architecture of File Size: 1MBPage Count: 12Explore further(PDF) Lecture Notes on Computer Architecturewww.researchgate.netComputer Architecture - an overview ScienceDirect Topicswww.sciencedirect.comWhat is Computer Architecture? - Definition from Techopediawww.techopedia.com1. An Introduction to Computer Architecture - Designing .www.oreilly.comWhat is Computer Architecture? - University of Washingtoncourses.cs.washington.eduRecommended to you b

Evolution 2250e and Evolution 3250e are equipped with a 2500 VApower supply. The Evolution 402e and Evolution 600e are equipped with a 4400 VA power supply, and the Evolution 403e and Evolution 900e house 6000 VA power supplies. Internal high-current line conditioning circuitry filters RF noise on the AC mains, as well as