Verilog Hdl A Guide To Digital Design And Synthesis-PDF Free Download

Verilog-A HDL Overview 1.1 Overview This Verilog-A Hardware Description Language (HDL) language reference manual defines a behavioral language for analog systems. Verilog-A HDL is derived from the IEEE 1364 Verilog HDL specification. This document is intended to cover the definition and semantics of Verilog-A HDL as proposed by Open Verilog .

1. On the File menu, click New. 2. In the New dialog box, select the type of design file corresponding to the type of HDL you want to use, SystemVerilog HDL File, VHDL File, or Verilog HDL File. 3. Right-click in the HDL file and then click InsertTemplate. 4. In the InsertTemplate dialog box, expand the section corresponding to the appropriate HDL, then expand the FullDesigns section.

Verilog Hardware Descriptive Language 5th edition, Donald Thomas, Philip Moorby, 2002,Kluwer Academic. Verilog HDL, A guide to digital design and synthesis, Samir Palnitkar, Sun Soft Press Verilog HDL Synthesis ( A practical primer ), J Bhasker, Star galaxy publishing Verilog

Verilog HDL model of a discrete electronic system and synthesizes this description into a gate-level netlist. FPGA Compiler II / FPGA Express supports v1.6 of the Verilog language. Deviations from the definition of the Verilog language are explicitly noted. Constructs added in versions subsequent to Verilog 1.6 might not be supported.

Verilog PLI Tutorial ? : 20% Complete What's new in Verilog 2001? : 50% Complete Verilog Quick Reference. Verilog in One Day : This tutorial is in bit lighter sense, with humor, So take it cool and enjoy. INTRODUCTION Introduction. Verilog is a HARDWARE DESCRIPTION LANGUAGE (HDL). A hardware

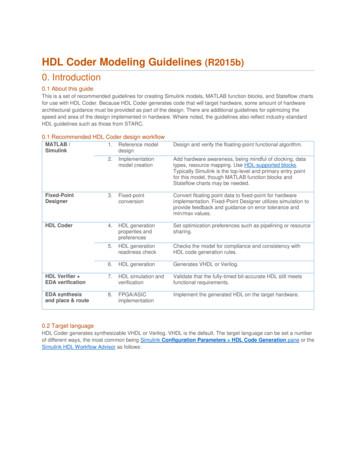

Implement the generated HDL on the target hardware. 0.2 Target language HDL Coder generates synthesizable VHDL or Verilog. VHDL is the default. The target language can be set a number of different ways, the most common being Simulink Configuration Parameters HDL Code Generation pane or the Simulink HDL Workflow Advisor as follows:

an independent Verilog consultant, specializing in providing comprehensive expert training on the Verilog HDL, SystemVerilog and PLI. Stuart is a co-authorof thebooks "SystemVerilogfor Design", "Verilog-2001: A Guide to theNewFeatures in the Verilog Hardware Description Language" and

Verilog vs. VHDL –Verilog is relatively simple and close to C –VHDL is complex and close to Ada –Verilog has 60% of the world digital design market (larger share in US) Verilog modeling range –From gates to proc

L3: Introduction to L3: Introduction to Verilog (Combinational Logic) Courtesy of Rex Min. Used with permission. Verilog References: Samir Palnitkar, Verilog HDL, Pearson Education (2nd edition). Donald Thomas, Philip Moorby, The Verilog Hardware Description Lang

6 Verilog HDL Quick Reference Guide 4.8 Logic Values Verilog uses a 4 value logic system for modeling. There are two additional unknown logic values that may occur internal to the simulation, but which cannot be used for modeling. 4.9 Logic Strengths Logic values can have 8 strength levels: 4 driving, 3 capacitive, and high impedance (no strength).

Samir Palnitkar SunSoft Press A Prentice Hall Title . Table of Contents About the Author v Foreword xxxv Preface xxxvii Acknowledgments xli Part 1: Basic Verilog Topics 1 1. Overview of Digital Design with Verilog HDL 3 . xiv Verilog HDL: A Guide to Dig

The Verilog Golden Reference Guide is a compact quick reference guide to the Verilog hardware description language, its syntax, semantics, synthesis and application to hardware design. The Verilog Golden Reference Guide is not intended as a replacement for the IEEE Standard Verilog Language Reference Manual.

ECE 232 Verilog tutorial 6 HDL Overview Hardware description languages (HDL) offer a way to design circuits using text-based descriptions HDL describes hardware using keywords and expressions. Representations for common forms »Logic expressions, truth tables, functions, logic gates

An Introduction to Verilog HDLHDL Alireza Ejlali. ٢ Textbook Verilog HDL A guide to Digital Design and Synthesis Samir Palnitkar SunSoft Press 1996. . not n1(d, q); // not is

Open Verilog International, Programming Language Interface Reference Manual, Los Gatos, CA, 1996 Palnitkar S., Verilog HDL, A Guide to Design and Synthesis, SunSoft Press, Sun

Compiler assembly code binary machine code Synthesis tool: HDL source gate-level specification hardware . ICARUS Verilog needs plenty of Verilog-2001 compliance - work in . bit serial adder Carry logic Cout Cin X Y Z Delay 1-bit Clk Rst D Flip Flop

Verilog HDL 7 Edited by Chu Yu Different Levels of Abstraction Architecture / Algorithmic (Behavior) A model that implements a design algorithm in high-level language construct A behavioral representation describes how a parti

Verilog References: Samir Palnitkar, Verilog HDL, Pearson Education (2nd edition). Donald Thomas, Philip Moorby, The Verilog Hardware Description Language, Fifth Edition, Kluwer Academic Publisher

Not listed in this paper — refer to the 1364-2001 Verilog Language Reference Manual (LRM) Part 1-10 L H D Sutherland Support For Verilog-2001 Several simulator and synthesis companies are working on adding support for the Verilog-2001 enhancements Simulators: Model Technology ModelSim — currently supports most new features

Verilog code thinks it is calling a native Verilog task or function Using the SystemVerilog DPI – Verilog code can directly call C functions – Verilog code can dire

familiar with Verilog-A should consult the books by Patrick and Miller [2] and Kundert and Zinke [3]. Details of the latest version of the Verilog-A language can also be found in the Verilog-A language reference manual [4]. Qucs first used the ADMS Verilog-A compiler in October 2006. At that time a series of complex changes had to be made .

In this tutorial we decided to use Verilog language so make sure it set correctly. Simulator language you can keep unchanged. Simple VERILOG example using VIVADO 2015 with ZYBO FPGA board . ZYBO Reference Manual Simple VERILOG example using VIVADO 2015 with ZYBO FPGA board v 0.1 SIMPLE VERILOG EXAMPLE USING VIVADO 2015 WITH ZYBO FPGA BOARD V .

CSE 371 (Roth): Verilog Primer 5 And now Verilog Structural Verilog: use for actual designs Wires and wire assignment Combinational primitives Hierarchical modules Timing Behavioral Verilog: use for wrappers and testing only I.e., things you don't want to write gate-level designs for Registers and memories

Everything about Verilog for this Course 1.Only allowed to use a very basic set of Verilog; see Verilog rules 2.Verilog cheatsheetby Karuas a quick reference of syntax; also includes the rules in it 3.Additional filename convention rules: Exactly one module per file, file named module_name.v

blockage forms in a narrowed artery, heart attack or stroke can result. High-Density Lipoprotein (HDL) or Good Cholesterol - The Bad Cholesterol Eater About one-fourth to one-third of blood cholesterol is carried by HDL. HDL cholesterol is known as "good" cholesterol, because high levels of HDL seem to protect against heart attack.

Scicos-HDL (v 0.4) Tutorial Scicos-HDL Tutorial 0.4 1 Scicos-HDL is a tool to design digital circuit system; it integrates the hardware circuit, algorithm and Scilab/Scicos environment as a plat for digital circuit design, simulation and Hardware Description Language generation. We

Digital Design EE 4490 Course Syllabus for Fall 2018 . Verilog HDL, and FPGA prototyping boards. Demonstrate the ability to modify existing HDL code to meet new system require- . the use of an inexpensive student-owned \Basys 3 Artix-7 FPGA Trainer Board" manufactured by Digilent,

Verilog HDL 15EC53 Dept. of ECE 2 Text Books: 1. Samir Palnitkar, “Verilog HDL: A Guide to Digital Design and Synthesis”, Pearson Education, Second Edition. 2. Kevin Skahill, “VHDL for Programmable Logic”, PHI/Pearson education, 2006. Reference Books:

Model the digital system using Verilog HDL. Text Books : 1 John P. Uyemura, “Chip Design for Submicron VLSI: CMOS layout and simulation”, Cengage Learning India Private Ltd, 11th Indian Reprint 2013. 2 Samir Palnitkar, “Verilog HDL A Guide to Digital Design and Synthesis”,

Xilinx ISim is a Hardware Description Language (HDL) simulator that lets you perform behavioral and timing simulations for VHDL, Verilog, and mixed VHDL/Verilog language designs. This document describes the ISim tool features, lists the HDL languages that ISim supports, and explains the methods of interfacing with the tool. For easier navigation

The Verilog HDL coding standards pertain to virtual component (VC) generation and deal with naming conventions, documentation of the code and the format, or style, of the code. Conformity to these standards simplifies reuse by describing insight that is absent fr om the code, making the code more readable and as-

3.Verilog HDL – Samir Palnitkar, 2nd Edition, Pearson Education, 2009. 4.Advanced Digital Design with Verilog HDL – Michael D. Ciletti, PHI, 2009. 3. Vision of the Department To impart quality technical education in

Verilog 2005 (IEEE Standard 1364-2005) consists of minor corrections, spec clarifications, and a few new language features SystemVerilog is a superset of Verilog-2005, with many new features and capabilities to aid design-verification and design-modeling

Verilog uses C like syntax – very concise. VHDL is strongly typed. Verilog: “Most widely used Hardware Description Language in the U.S.” (someone at Harvard but the web page was moved). “In the United States, the commercial indust

Verilog Language Features Verilog supports 4 value levels: Data Values Value Level Represents 0 Logic 0 state 1 Logic 1 state x Unknown logic state z High impedance state All unconnected ne

is project will give you a basic understanding of ModelSim and the Verilog hardware description language (HDL). ModelSim is an IDE for hardware design which provides behavioral simulation of a number of languages, i.e., Verilog, VHDL, a

SystemVerilog is a superset of another HDL: Verilog –Familiarity with Verilog (or even VHDL) helps a lot Useful SystemVerilog resources and tutorials on the course project web page –Including a link to a good Verilog tutori

1. National Instruments’ Digital Electronics FPGA Board user manual 2. Verilog HDL books Stephen Brown, Zvonko G. Vranesic, “Fundamentals of Digital Logic with Verilog Design”, 2002 Zainalabedin Navabi, “Verilog Digital Systems Design: RT Level Synthesis, Testbench, and Verification”, 2005

Verilog, System Verilog or Bluespec. As systems become more complex, more effort is required to achieve a reliable model of the system. In this situation a high level HDL can speed up the modelling process as well as producing a more reliable design. Bluespec is able to model computer architecture at a high level of abstraction as well as guarantee

Verilog Stored Number Verilog Stored Number 4’b1001 1001 4’d5 0101 8’b1001 0000 1001 12’hFA3 1111 1001 0011 8’b0000_1001 0000 1001 8’o12 00 001 010 8’bxX0X1zZ1 XX0X 1ZZ1 4’h7 0111 ‘b01 0000 . 0001 12’h0 0000 0000 0000. Carnegie Mellon 11 Precedence of Operations in Verilog Highest NOT