Verilog HDL Reference Manual - Pub.ro

FPGA Compiler II /FPGA ExpressVerilog HDLReference ManualVersion 1999.05, May 1999Comments?E-mail your comments about Synopsysdocumentation to doc@synopsys.com

Copyright Notice and Proprietary InformationCopyright 1999 Synopsys, Inc. All rights reserved. This software and documentation are owned by Synopsys, Inc., andfurnished under a license agreement. The software and documentation may be used or copied only in accordance with the terms ofthe license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or byany means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expresslyprovided by the license agreement.Right to Copy DocumentationThe license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only.Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee mustassign sequential numbers to all copies. These copies shall contain the following legend on the cover page:“This document is duplicated with the permission of Synopsys, Inc., for the exclusive use ofand its employees. This is copy number.”Destination Control StatementAll technical data contained in this publication is subject to the export control laws of the United States of America.Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader’s responsibility todetermine the applicable regulations and to comply with them.DisclaimerSYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITHREGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OFMERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.Registered TrademarksSynopsys, the Synopsys logo, BiNMOS-CBA, CMOS-CBA, COSSAP, DESIGN (ARROWS), DesignPower, DesignWare,dont use, Eagle Design Automation, ExpressModel, in-Sync, LM-1000, LM-1200, Logic Modeling, Logic Modeling(logo), Memory Architect, ModelAccess, ModelTools, PathMill, PLdebug, Powerview, Retargeter, SmartLicense,SmartLogic, SmartModel, SmartModels, SNUG, SOLV-IT!, SourceModel Library, Stream Driven Simulator ,Synopsys, Synopsys (logo), Synopsys VHDL Compiler, Synthetic Designs, Synthetic Libraries, TestBench Manager,TimeMill, ViewBase, ViewData, ViewDoc, ViewDraw, ViewFault, ViewFlow, VIEWFPGA, ViewGen, Viewlogic,ViewPlace, ViewPLD, ViewScript, ViewSim, ViewState, ViewSynthesis, ViewText, Workview, Workview Office, andWorkview Plus are registered trademarks of Synopsys, Inc.Trademarks3-D Debugging, AC/Grade, AMPS, Arcadia, Arkos, Aurora, BCView, BOA, BRT, CBA Design System,CBA-Frame, characterize, Chip Architect, Chronologic, Compiler Designs, Core Network, Core Store, Cyclone, DataPath Express, DataPath Architect, DC Expert, DC Expert Plus, DC Professional, Delay Mill, Design Advisor, DesignAnalyzer proposed, Design Exchange, Design Source, DesignTime, DesignWare Developer, Direct RTL, DirectSilicon Access, dont touch, dont touch network, DW 8051, DWPCI, DxDataBook, DxDataManager, Eagle, Eaglei,Eagle V, Embedded System Prototype, Floorplan Manager, Formality, FoundryModel, FPGA Compiler II, FPGAExpress, Fusion, FusionHDL, General Purpose Post-Processor, GPP, HDL Advisor, HTX, Integrator, IntelliFlow,Interactive Waveform Viewer, ISIS, ISIS PreVUE, LM-1400, LM-700, LM-family, Logic Model, ModelSource,ModelWare, MOTIVE, MS-3200, MS-3400, PathBlazer, PDQ, POET, PowerArc, PowerCODE, PowerGate, PowerMill,PreVUE, PrimeTime, Protocol Compiler, QUIET, QUIET Expert, RailMill, RTL Analyzer, Shadow Debugger, SiliconArchitects, SimuBus, SmartCircuit, SmartModel Windows, Source-Level Design, SourceModel, SpeedWave, SWIFT,SWIFT interface, Synopsys Behavioral Compiler, Synopsys Design Compiler, Synopsys ECL Compiler, SynopsysECO Compiler, Synopsys FPGA Compiler, Synopsys Frame Compiler, Synopsys Graphical Environment, SynopsysHDL Compiler, Synopsys Library Compiler, Synopsys ModelFactory, Synopsys Module Compiler, Synopsys PowerCompiler, Synopsys Test Compiler, Synopsys Test Compiler Plus, TAP-in, Test Manager, TestGen, TestGen ExpertPlus, TestSim, Timing Annotator, TLC, Trace-On-Demand, VCS, DCS Express, VCSi, VHDL System Simulator,ViewAnalog, ViewDatabook, ViewDRC, ViewLibrarian, ViewLibrary, ViewProject, ViewSymbol, ViewTrace, Visualyze,Vivace, VMD, VSS Expert, VSS Professional VWaves, XFX, XNS, and XTK are trademarks of Synopsys, Inc.Service MarksSolvNET is a service mark of Synopsys, Inc.All other product or company names may be trademarks of their respective owners.Printed in the U.S.A.FPGA Compiler II / FPGA Express Verilog HDL Reference Manual, Version 1999.05ii

About This ManualThis manual describes the Verilog portion of Synopsys FPGACompiler II / FPGA Express application, part of the Synopsys suiteof synthesis tools. FPGA Compiler II / FPGA Express reads an RTLVerilog HDL model of a discrete electronic system and synthesizesthis description into a gate-level netlist.FPGA Compiler II / FPGA Express supports v1.6 of the Veriloglanguage. Deviations from the definition of the Verilog language areexplicitly noted. Constructs added in versions subsequent to Verilog1.6 might not be supported. Aspects of the Verilog language that arenot supported are listed in Appendix B.AudienceThis manual is written for logic designers and electronic engineerswho are familiar with Synopsys synthesis products. Knowledge of theVerilog language is required, and knowledge of a high-levelprogramming language is helpful.iii

Other Sources of InformationThe resources in the following sections provide additional information: Related Publications SolvNET Online Help Customer SupportRelated PublicationsThese Synopsys documents supply additional information: FPGA Compiler II / FPGA Express Getting Started Manual Design Compiler Command-Line Interface Guide Design Compiler Reference Manual: Constraints and Timing Design Compiler Reference Manual: Optimization and TimingAnalysis Design Compiler Tutorial Design Compiler User Guide DesignWare Developer Guide VSS User GuideMan PagesYou can view man pages from fc2 shell / fe shell environment. Fromthe shell prompt, enter:iv

fc2 shell help command nameorfe shell help command nameSolvNET Online HelpSOLV-IT! is the Synopsys electronic knowledge base. It containsinformation about Synopsys and its tools and is updated daily.Access SOLV-IT! through e-mail or through the World Wide Web(WWW). For more information about SOLV-IT!, send e-mail tosolvitfb@synopsys.comor view the Synopsys Web page athttp://www.synopsys.comCustomer SupportIf you have problems, questions, or suggestions, contact theSynopsys Technical Support Center in one of the following ways: Send e-mail tosupport center@synopsys.com Call (650) 584-4200 outside the continental United States or call(800) 245-8005 inside the continental United States, from 7 a.m.to 5:30 p.m. Pacific time, Monday through Friday. Send a fax to (650) 584-2539.v

ConventionsThe following conventions are used in Synopsys documentation.Conventioncouriercourier italiccourier bold[ ] DescriptionIndicates command syntax.In command syntax and examples, showssystem prompts, text from files, errormessages, and reports printed by thesystem.Indicates a user specification, such asobject nameIn command syntax and examples, indicatesuser input (text the user types verbatim).Denotes optional parameters, such as pin1[pin2, . . pinN]Indicates a choice among alternatives, suchaslow medium high(Ctrl-c)\/Edit CopyviThis example indicates that you can enterone of three possible values for an option:low, medium, or high.Connects two terms that are read as a singleterm by the system. For example,design space.Indicates a keyboard combination, such asholding down the Ctrl key and pressing c.Indicates a continuation of a command line.Indicates levels of directory structure.Shows a menu selection. Edit is the menuname and Copy is the item on the menu.

Table of ContentsAbout This Manual1. FPGA Compiler II / FPGA Express with Verilog HDLHardware Description Languages . . . . . . . . . . . . . . . . . . . . . . . . . .1-2FPGA Compiler II / FPGA Express and the Design Process . . . . .1-4Using FPGA Compiler II / FPGA Express to Compile a Verilog HDL Design1-5Design Methodology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-62. Description StylesDesign Hierarchy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2Structural Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3Functional Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3Mixing Structural and Functional Descriptions . . . . . . . . . . . . . . . .2-4Design Methodology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6Description Style . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6Language Constructs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6vii

Register Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7Asynchronous Designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-83. Structural DescriptionsModules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-2Macromodules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3Port Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-4Port Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-5Renaming Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6Module Statements and Constructs . . . . . . . . . . . . . . . . . . . . . . . .3-7Structural Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .parameter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .wire. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .wand. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .wor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .tri . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .supply0 and supply1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .reg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-83-83-93-103-113-123-133-13Port Declarations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .inout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-143-143-143-15Continuous Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15Module Instantiations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17Named and Positional Notation . . . . . . . . . . . . . . . . . . . . . . . . . 3-18Parameterized Designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19viii

Gate-Level Modeling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20Three-State Buffer Instantiation . . . . . . . . . . . . . . . . . . . . . . . . . 3-224. ExpressionsConstant-Valued Expressions . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2Operators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3Arithmetic Operators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4Relational Operators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5Equality Operators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-6Handling Comparisons to X or Z . . . . . . . . . . . . . . . . . . . . . . . .4-7Logical Operators. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8Bitwise Operators. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-9Reduction Operators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10Shift Operators. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11Conditional Operator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12Concatenation Operators. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13Operator Precedence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15Operands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16Wires and Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17Bit-Selects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17Part-Selects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18Function Calls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18Concatenation of Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19Expression Bit-Widths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19ix

5. Functional DescriptionsSequential Constructs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-2Function Declarations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-3Input Declarations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-5Output From a Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-5Register Declarations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-6Memory Declarations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-7Parameter Declarations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8Integer Declarations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-9Function Statements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-9Procedural Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10RTL Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11begin.end Block Statements . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14if.else Statements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15Conditional Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18case Statements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18Full Case and Parallel Case. . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20casex Statements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22casez Statements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25for Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27while Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29forever Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30disable Statements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31task Statements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32always Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34x

Event Expression . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34Incomplete Event Specification . . . . . . . . . . . . . . . . . . . . . . . . . 5-376. Register and Three-State InferenceRegister Inference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-1The Inference Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-2Latch Inference Warnings . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4Controlling Register Inference . . . . . . . . . . . . . . . . . . . . . . . . . .Attributes That Control Register Inference . . . . . . . . . . . . . .6-46-4Inferring Latches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7Inferring SR Latches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7Inferring D Latches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9Understanding the Limitations of D Latch Inference . . . . . . 6-19Inferring Master-Slave Latches. . . . . . . . . . . . . . . . . . . . . . . 6-19Inferring Flip-Flops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Inferring D Flip-Flops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Understanding the Limitations of D Flip-Flop Inference . . . .Inferring JK Flip-Flops . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Inferring Toggle Flip-Flops . . . . . . . . . . . . . . . . . . . . . . . . . .Getting the Best Results. . . . . . . . . . . . . . . . . . . . . . . . . . . .6-216-216-356-376-416-46Understanding Limitations of Register Inference . . . . . . . . . . . . 6-50Three-State Inference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-51Reporting Three-State Inference . . . . . . . . . . . . . . . . . . . . . . . . 6-51Controlling Three-State Inference . . . . . . . . . . . . . . . . . . . . . . . 6-51Inferring Three-State Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-52Simple Three-State Driver . . . . . . . . . . . . . . . . . . . . . . . . . . 6-52Registered Three-State Drivers . . . . . . . . . . . . . . . . . . . . . . 6-57xi

Understanding the Limitations of Three-State Inference . . . . . . 6-607. Writing Circuit DescriptionsHow Statements Are Mapped to Logic . . . . . . . . . . . . . . . . . . . . . .7-2Design Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3Using Design Knowledge. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-7Optimizing Arithmetic Expressions . . . . . . . . . . . . . . . . . . . . . . 7-7Arranging Expression Trees for Minimum Delay. . . . . . . . . . 7-7Sharing Common Subexpressions . . . . . . . . . . . . . . . . . . . . 7-12Using Operator Bit-Width Efficiently. . . . . . . . . . . . . . . . . . . . . . 7-15Using State Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16Describing State Machines . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19Minimizing Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-24Separating Sequential and Combinational Assignments . . . . . . 7-27Don’t Care Inference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-28Limitations of Using Don’t Care Values . . . . . . . . . . . . . . . . . . . 7-29Differences Between Simulation and Synthesis. . . . . . . . . . . . . 7-29Propagating Constants . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-31Synthesis Issues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-31Feedback Paths and Latches. . . . . . . . . . . . . . . . . . . . . . . . . . . 7-32Synthesizing Asynchronous Designs. . . . . . . . . . . . . . . . . . . . . 7-32Designing for Overall Efficiency. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-34Describing Random Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-35Sharing Complex Operators . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-35xii

8. FPGA Compiler II / FPGA Express DirectivesNotation for FPGA Compiler II / FPGA Express Directives . . . . . . .8-2translate off and translate on Directives . . . . . . . . . . . . . . . . . . . .8-2parallel case Directive . . . . . . . . . . . . . . .

Verilog HDL model of a discrete electronic system and synthesizes this description into a gate-level netlist. FPGA Compiler II / FPGA Express supports v1.6 of the Verilog language. Deviations from the definition of the Verilog language are explicitly noted. Constructs added in versions subsequent to Verilog 1.6 might not be supported.

Verilog-A HDL Overview 1.1 Overview This Verilog-A Hardware Description Language (HDL) language reference manual defines a behavioral language for analog systems. Verilog-A HDL is derived from the IEEE 1364 Verilog HDL specification. This document is intended to cover the definition and semantics of Verilog-A HDL as proposed by Open Verilog .

1. On the File menu, click New. 2. In the New dialog box, select the type of design file corresponding to the type of HDL you want to use, SystemVerilog HDL File, VHDL File, or Verilog HDL File. 3. Right-click in the HDL file and then click InsertTemplate. 4. In the InsertTemplate dialog box, expand the section corresponding to the appropriate HDL, then expand the FullDesigns section.

Verilog PLI Tutorial ? : 20% Complete What's new in Verilog 2001? : 50% Complete Verilog Quick Reference. Verilog in One Day : This tutorial is in bit lighter sense, with humor, So take it cool and enjoy. INTRODUCTION Introduction. Verilog is a HARDWARE DESCRIPTION LANGUAGE (HDL). A hardware

Verilog Hardware Descriptive Language 5th edition, Donald Thomas, Philip Moorby, 2002,Kluwer Academic. Verilog HDL, A guide to digital design and synthesis, Samir Palnitkar, Sun Soft Press Verilog HDL Synthesis ( A practical primer ), J Bhasker, Star galaxy publishing Verilog

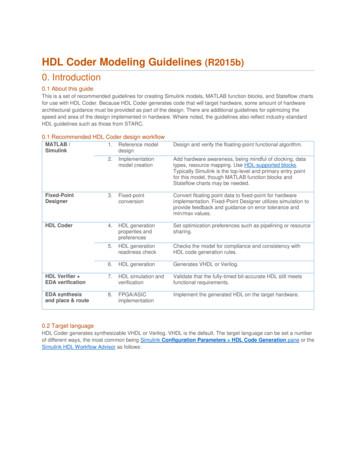

Implement the generated HDL on the target hardware. 0.2 Target language HDL Coder generates synthesizable VHDL or Verilog. VHDL is the default. The target language can be set a number of different ways, the most common being Simulink Configuration Parameters HDL Code Generation pane or the Simulink HDL Workflow Advisor as follows:

The Verilog Golden Reference Guide is a compact quick reference guide to the Verilog hardware description language, its syntax, semantics, synthesis and application to hardware design. The Verilog Golden Reference Guide is not intended as a replacement for the IEEE Standard Verilog Language Reference Manual.

an independent Verilog consultant, specializing in providing comprehensive expert training on the Verilog HDL, SystemVerilog and PLI. Stuart is a co-authorof thebooks "SystemVerilogfor Design", "Verilog-2001: A Guide to theNewFeatures in the Verilog Hardware Description Language" and

ALBERT WOODFOX . CIVIL ACTION NO. 06-789-JJB-RLB . VERSUS . BURL CAIN, WARDEN OF THE LOUISIANA . STATE PENITENTIARY, ET AL. RULING . Before this Court is the pending Motion (doc. 279) for Rule 23(c) release of Petitioner, Albert Woodfox. Briefs were filed in response to this motion and were considered by this Court. Subsequently, a motion hearing on this matter was held before this Court on .