Interrupts And Stack Intro - UTEP

Interrupts and Stack IntroEE3376

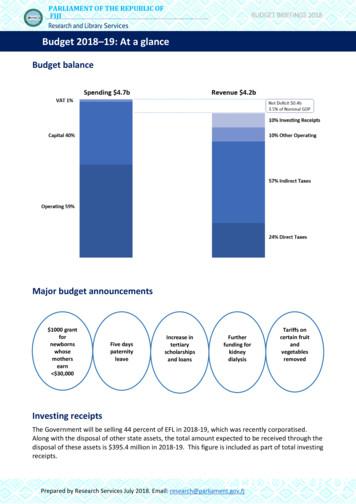

Intro to Stackl l l l Last In – First Out LIFO structure with hardware assistl Dedicated SP pointing to TOSl One push instruction and one emulated pop instructionl All other addressing modes work as wellMust be initialized in ASM but handled under the covers for Cl The first address loaded in SP is never used.Usedl for local (temporary) variablesl for saving snapshot of registers to use temporarilyl for saving the PC and SR during interruptsGenerally just a great way to save things for short periodl Can easily de-allocate memory for other use

Intro to Stack - Push

Intro to Stack - Example

Intro to Stack - Pop

Example of Stack usage

Example of local variables

InterruptsSystem-On-Chip lsA/D converterSerialParallelTimePWMConsolidatedMemory

Interrupt Overviewl l l l Interrupts (a.k.a. exceptions) are requests to the CPUTypical example is hardware requesting serviceAvoids wasteful polling – CPU is unproductive during polling.Some sources of interrupts are intentionall l l l from internal sources (i.e. Timer or ADC sample completion)from external sources (i.e. NMI pin)from reset assertion (highest priority)Some sources of interrupts are not necessarily intentionall from instructions (i.e. illegal instruction - trap)from a variety of illegal hardware conditions (bad clock or Vdd)l Watch Dog Timeoutl l When they will occur is unknown to the CPU – asynchronousDifferent priority levels for interruptsl Most interrupts are mask-able and need to be armed.l

Interrupt Service Routine (Handler)l Interrupt cause the ISR to be executed when –––the interrupt is armed (interrupt specific arm bit is set – P1IE)interrupts in general are enabled (GIE is set in SR)and the interrupt signal is asserted (either internally or externally)l For each type of interrupt, there is an entry in the interrupt vectorl An Interrupt Service Routine (ISR) is like a special subroutine.–––––current instruction in main program is completedtypically need to clear the interrupt source with an acknowledgeexecute an rti instruction (not an rts for subroutine)all registers are restored after executionmain program resumes as if nothing happened

Interrupt Activities

RETI instruction

Interrupt Vector Table

Interrupt Examplesl Servicing data transfers for data communication peripherals–––l To perform periodic tasks using Timer interrupts––l Blinking LED (once a second)LCD display update (60 Hz)To handle unexpected software or hardware problems–––l UART buffer full and transmit completeUART receive buffer full and transmit completeIICmissing clocklow Vddbad instructionReset is a fundamental interrupt requesting to start over–Unmaskable, highest priority and no reti

Interrupt flow

Interrupt Prioritiesl For real time embedded systems, some interrupts have to behandled in a specific amount of time (real time constraint)l Analog has hard timing requirementsl Anti-lock brakes in a car need sense of urgencyl Playing Tetris – not so important – humans are slowl These interrupts get priority and can interrupt current interrupts.l Maskable interrupts also have individual bits that should set firstl GIE enables all maskable interruptsl l This bit should be set last at the end of the configurationIndividual bits control the (non)-maskable interruptsl non is in parenthesis because technically they can be maskedl Just not affected globally with the GIE bit.

MSP430 Priorities

Interrupt Flowisr2:entry:isr1:one time lessloop)retireti

Stack Pushing Prior to Interruptl Processors can take two approaches for “saving context”l Save everything – safer – all registers stacked - Motorolal Save minimum – let user save anything that could changel Faster - MSP430 uses the second approach so beware.

Stack Pushing Prior to Interruptl l l l l PC is pushed on stackSR is pushed on stackSR is cleared (GIE and low power modes remembered)Jump to Interrupt Handler location described in Interrupt VectorGIE is turned off for during handler

Interrupt Acknowledgingl Must clear the flag of any interrupt during the handlerl Otherwise, you will repeat the interruptl Other processors usually require clearing the flagl MSP430l No requirement for acknowledging for single source IRQsl For multi-source IRQs – Timer for instance – you will mustclear manually

Interrupt Synchronizationl Different software threads are executing––main program is considered foreground threadinterrupts are background threadsl Global variables are used to communicate between theml Global variables have dedicated space in SRAMl Different global data structures can be used–––l mail boxFIFOlinked listLocal variables are not allowed for passing data.–can’t use the stack because the threads are asynchronous

Nested Interrupt FlowNMIIRQmain programISRISRISRNMIThree software threads with only one active at a time.Interrupts are a hardware mechanism to switch between threads.To get second maskable interrupt in interrupt, the first handlermust enable GIE. NMI will always interrupt a maskable interrupt.

First-In First Out (FIFO) data structurel l FIFOs are useful structures for consumer-producer applicationsconsumer-producer apps–––l l Some finite amount of memory is dedicated to FIFOTwo pointers are used–––l l l data flow in one directionorder of data is importantallows producer to get X bytes ahead of consumer without problem.get pointer – controlled by the consumer (main program)put pointer – controlled by the producer (interrupt handler)get pointer chases put pointerPointers wrap around to the beginning if they extend boundaryIf get pointer put pointer after a get, FIFO emptyIf get pointer put pointer after a put, FIFO overflow

First-In First Out (FIFO) data tempty

Interrupt Service Routine (Handler) ! Interrupt cause the ISR to be executed when – the interrupt is armed (interrupt specific arm bit is set – P1IE) – interrupts in general are enabled (GIE is set in SR) – and the interrupt signal is asserted (either internally or externally) For each typ

Before you can use a stack you have to initialize the SP to point to one value higher than the highest memory location in the stack. For the HC12 use a block of memory from about 3B00 to 3BFF for the stack. For this region of memory, initialize the stack pointer to 3C00. Use LDS (Load Stack Pointer) to initialize the stack pointer.

Program Syllabus Course name: HEALTH EDUCATION FOR ELEMENTARY SCHOOL TEACHERS Course no.: HSCI 4101-001 Course CRN: 27187 Semester/year SPRING 2017 . {TExES} Preparation Manual // Core Subjects EC-6 Exam # 291 UTEP HELP DESK 747-5247 Off - Campus Email: HELPDESK@UTEP.EDU UTEP HELP DESK { On Campus } 4357 @ UTEP Library Room 300 .

Chapter 4. Interrupts and Exceptions An interrupt is usually defined as an event that alters the sequence of instructions executed by a processor. Such events correspond to electrical signals generated by hardware circuits both inside and outside the CPU chip. Interrupts are often divided into synchronous and asynchronous interrupts :

The Stack Topology displays whether the topology of the stack is chain or ring. In this example, the topology is Chain. The Stack Active switch displays the unit ID of the Active unit of the stack. In this example, the switch being configured (Unit 1) is the Active of the stack. Step 3. Click at least two ports to configure as stacking ports.

The Stack Topology displays whether the topology of the stack is chain or ring. In this example, the topology is Chain. The Stack Active switch displays the unit ID of the Active unit of the stack. In this example, the switch being configured (Unit 1) is the Active of the stack. Step 3. Click at least two ports to configure as stacking ports.

Text/HTML General Information Welcome to the University of Texas at El Paso (UTEP)! This undergraduate catalog contains information about UTEP’s success in combining academic and research excellence with innovative programs and services, outstanding faculty, and a university-wide commitment to fostering student success.

leader among Hispanic-serving institutions, UTEP is committed to the ideals of access and excellence. With an enrollment of nearly 20,000 students, UTEP is a national leader in the study of Latin American and U.S. Hispanic history, literature, and culture. 500 West University Avenue El Paso, Texas 79968 915-747-5000 www.utep.edu

appropriate strategies to solve problems. Mathworld.com Classification: Number Theory Diophantine Equations Coin Problem 02-02. 14 AMC 8 Practice Questions Continued -Ms. Hamilton’s eighth-grade class wants to participate intheannualthree-person-teambasketballtournament. The losing team of each game is eliminated from the tournament. Ifsixteenteamscompete, howmanygames will be played to .