Cost Per Wafer - Smithsonian Institution

2Cost Per Wafer

2Cost Per WaferCost per wafer is perhaps the most widelyused cost metric in the semiconductor industry. Its value lies in the ability to combinelarge quantities of cost data and obtain oneindicator of operating cost that can be used tocompare different pieces of equipment, different processes, alternative materials, etc. Costper wafer can also be used as a benchmarkingmetric (see Chapter 4, Fab Benchmarking). Itcan further be used to estimate a fair price forfoundry-produced wafers.Information from the SemiconductorIndustry Association in the U.S. indicatesthat average cost per wafer has increased by3X over the last 15 years (Figure 2-1).Although the cost of labor, materials andcapital expenditures per wafer haveincreased, the real cost of manufacturingsemiconductor chips continues to decreasebecause the number of transistors that can beplaced on a wafer has grown faster thanmanufacturing costs, as shown in Figure 2-2.equipment and operations. By continuallydecreasing or controlling cost per wafer, ICmanufacturers can increase profitability.Cost per wafer at the fab level can be simplycomputed using the total cost of manufacturing divided by the total number of yieldedwafers produced. Cost per wafer at theequipment level is typically computed Òfromthe ground-upÓ using the cost of equipmentdepreciation, cost of direct labor, maintenance and materials, cost of energy and otherfacilities as well as building depreciationcosts.As discussed in Chapter 1, this ever-increasing cost per wafer is offset by the ability toshrink feature size by 30 percent eachdevice generation, thereby decreasing themanufacturing cost per transistor. Theeffective price of DRAMs, measured in costper bit, falls by 30 percent per year. Risingmanufacturing cost is further offset by manufacturersÕ ability to continually increasedevice yields, transition to larger waferssizes and increase the productivity of fabCost per wafer first enjoyed widespread useseveral years following the introduction ofcost-of-ownership modeling by SEMATECH, the consortium of semiconductor manufacturers in the U.S. Cost per wafer is oftenused to compare the cost-of-ownership performance of competing pieces of equipment.It is also used by semiconductor manufacturers for benchmarking purposes, and toassess the cost of making process modifications and adopting new processes.Importantly, however, one of the most critical components in cost-of-ownership calculations is the yield of the given process step.Because yield influences cost so dramaticallyand because yield is very difficult to determine on a step-by-step basis, most COO calculations assume identical yields from oneprocess tool to another. For more discussionon COO see Chapter 4, Fab Benchmarking.INTEGRATED CIRCUIT ENGINEERING CORPORATION2-1

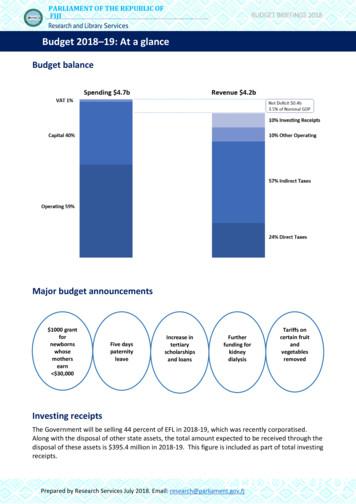

Cost Per WaferNon-LaborMfg 157(21.5%)Non-LaborMfg 994(41.9%)Mfg Cost ofGoods Sold 432(59.1%)S, G&A 158(21.6%)S, G&A 374(15.8%)R&D 257(10.8%)R&D 74(10.1%)Mfg Cost ofGoods Sold 1,268(53.4%)Depreciation 247(10.4%)Depreciation 67(9.2%)Taxes &Other 230(9.7%)Mfg Labor 275(37.6%)1980Total 731/150mm WaferMfg Labor 273(11.5%)1995Total 2,375/150mm Wafer*North American firms onlySource: SIA21075AFigure 2-1. Total Cost Per Wafer Start (1980 Versus 1995*)1,000ManufacturingCost Per WaferIndex (1982 100)100DRAMPrice Per Bit101Source: SIA198219831984198519861987 1988Year198919901991199219931994199522726Figure 2-2. How Decreasing Cost Per Bit Compensates for Increasing Manufacturing Cost2-2INTEGRATED CIRCUIT ENGINEERING CORPORATION

Cost Per WaferOperating CostsFab operating costs can be divided into fixedcosts and variable costs. Fixed costs includeequipment depreciation, R&D, overhead,and general and administrative costs. Themost important variable cost is the cost ofsales (manufacturing cost of goods sold),which includes the cost of consumables,spare parts, materials (including cleanroomgarments, etc.), labor, production control,and facilities (operating power for the plant,deionized water systems, etc.). The trend ofincreasing manufacturing cost of goods soldis shown in Figure 2-3. This cost of manufacturing wafers, without consideringincreasing depreciation costs, rises at anaverage rate of 5-6 percent per year.Operating costs are often defined for waferprocessing alone as assembly and final testing of devices are commonly performed at adifferent manufacturing sites, often inSoutheast Asian countries where labor costsare low by North American, Japanese, andEuropean standards. In rough terms, ICmanufacturing costs can be divided intothree categories consisting of: 10-15 percent due to labor cost, 35-40 percent due to materials costs(including starting wafer cost), and 40-50 percent for capital costs[1]1,3001,200150mm Equivalent Wafer1,1001,000Annual TrendGrowth 5.6%900800Mean7006005004001978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995Source: SIA22727Figure 2-3. Manufacturing Cost of Goods Sold (Less Depreciation) Per Wafer StartINTEGRATED CIRCUIT ENGINEERING CORPORATION2-3

Cost Per WaferBeyond these broad categories, operatingcosts are typically broken down into fourmain components: Manufacturing cost of devices sold (allcosts directly allocated to production, lessdepreciation), Selling, general and administrativeexpenses, Research and development costs, and Depreciation expenses.As shown in Figure 2-1, manufacturing costof goods sold in 1995 accounted for over 53percent of the total cost per wafer start formerchant IC producers in the U.S.[2] Cost perwafer for IC manufacturers has increasedfrom 1980Õs level of around 730 per 150mmequivalent wafer to 1995Õs level of nearly 2,400 per 150mm wafer. In other words, thecost per wafer has risen by over a factor ofthree in a fifteen year period. In addition, theportion of manufacturing costs due to laborexpenses has dropped dramatically.Interestingly, the dollar amount companieshad to devote to labor was almost exactly thesame in 1995 as it was in 1980.manufacturing costs and S, G&A costsincreased by almost a factor of 9 each; andsales by U.S.-based merchant semiconductorfirms increased by a factor of 12. As can begleaned from this illustration, during theindustryÕs most difficult period in the mid1980s, R&D and depreciation expendituresremained high while the sales index (annualsemiconductor sales) dipped too low to support these expenditures.In the most recent expansionary cyclebetween 1993 and 1996, the focus on increasing expenditures for equipment and newfabs has increased dramatically. However, asshown in Figure 2-5, depreciation expensesas a percent of sales appear to be stabilizing,despite a long-term average increase of 10-15percent per year.The following sections briefly discusses thecost components for manufacturing costs,depreciation, and R&D costs. Selling, general and administrative costs will not be covered as these expenditures vary a great dealfrom one company to the next, and vary littlefrom year to year for a given company.These expenditures can also be viewed relative to annual semiconductor industry sales.In other words, the rates of increase inexpenditures for manufacturing, R&D,depreciation, and S, G&A expenses can becompared to the rate of annual increases inoverall semiconductor industry revenues.Shown in Figure 2-4 are year-to-year valuesfor R&D, depreciation expenses, manufacturing costs, S, G&A costs, and semiconductor sales, normalized to 1978 values. Longterm, depreciation and R&D costs have risenmuch more dramatically than manufacturing costs, semiconductor sales, and S, G&Aexpenditures. Between 1978 and 1995,depreciation outlays increased by a factor of17; R&D costs increased by a factor of 14;R&D and Depreciation Costs2-4INTEGRATED CIRCUIT ENGINEERING CORPORATIONAs mentioned previously, due to theextremely high pace of technological innovation in this industry, necessary investmentfor R&D, new fabs, and equipment can be ashigh as 25-30 percent of sales. In fact, thepercentage of sales that must be reinvestedfor R&D in the semiconductor industry surpasses that needed in nearly every otherhigh technology industry (Figure 2-6).Interestingly enough, the key industries thatsemiconductors feedÑcomputers, consumerelectronics, communications, and automotiveÑeach requires lower investment todevelop than the chips that run them.

Cost Per Wafer18.015.0Mfg. Cost ofGoods SoldS, G&ADepreciation14.0R&D17.016.0Index: 1978 - 1.013.012.011.010.09.08.07.06.05.04.0Sales Index3.02.01.01978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995YearNote: U.S. merchant semiconductor manufacturers only.Source: SIA19783BFigure 2-4. Annual Expenditures for Major Cost ComponentsDepreciation as a Percent of Sales Revenue1614Median1210Mean8641978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995YearNote: U.S. merchant semiconductor manufacturers only.Source: SIA19784BFigure 2-5. Depreciation Expenses Rise More Rapidly Than IC RevenuesINTEGRATED CIRCUIT ENGINEERING CORPORATION2-5

Cost Per WaferSoftware and ,,,,,,,,,,,,Computer CommunicationsSemiconductorsHealth CareComputersElectronicsInstrumentsOffice Equipment(Excluding Computers)Aerospace and l ManufacturingElectrical Products02468101214R&D as a Percent of SalesSource: Business Week19781AFigure 2-6. R&D For Semiconductors Exceed Most Other High Technology IndustriesIn addition, as technology developmentbecomes more expensive, it becomes moredifficult to get a timely return on investment.Generally, IC manufacturers invest 10-15percent of sales each year in R&D. Figure 27 shows R&D expenditures both in billionsof dollars and as a percentage of sales revenues for merchant IC manufacturers in theUS. While this percentage appears to havedeclined over the 1992-1995 period, R&Doutlays rose dramatically at an averageannual rate of 18 percent over the period.The most important components in development costs are equipment costs and labor, asillustrated in Figure 2-8. One of the mostimportant strategies used by semiconductorcompanies to control these costs is the formation of strategic partnerships for bothtechnology development and in some cases,fab ownership.2-6INTEGRATED CIRCUIT ENGINEERING CORPORATIONAlso shown back in Chapter 1, the top 10companies accounted for 55 percent of allcapital spending in the semiconductor

Cost Per Waferindustry in 1996, and 83 percent of all spending is performed by 25 companies.Worldwide, SEMI and SEAJ estimate that63.5 percent of capital spending goes towardwafer processing equipment, 21 percenttoward testing equipment, nearly 10 percentto assembly equipment and nearly 6 percentto facility related equipment (i.e., computers,automation, etc.). These numbers equate to1996 market sizes of 26.6 billion for waferprocessing equipment, 8.8 billion for testingequipment, 4 billion for assembly equipment and 2.5 billion for facility equipment.6.018.05.55.016.0Billions of Dollars4.014.03.53.012.0Percentage of Sales2.5Billions of Dollars2.010.0Percent of Sales Revenues4.51.51.08.0Annual TrendGrowth 14.7%0.50.06.01978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995YearSource: SIA22728Figure 2-7. Semiconductor R&D ExpendituresOther (Including Travel)8%Consumables(Gases and Chemicals)16%Equipment31%Labor 26%Facilities and Property19%Source: Intel/EE Times19977AFigure 2-8. Breakdown of Semiconductor Technology Development CostsINTEGRATED CIRCUIT ENGINEERING CORPORATION2-7

Cost Per WaferDepreciation schedules vary from one country to another. Semiconductor firms in theU.S. have attempted to change 5-year depreciation schedules on semiconductor processing equipment to 3 years to better reflect therapid rate of technological obsolescence infabs today. Despite bipartisan support in theU.S. House of Representatives and Senate,the bill to change these depreciation schedules did not pass. However, some progresswas made in 1997 as a bill was passed toraise R&D tax credit for basic research from 8percent to 11 percent. The bill also allows a 6percent manufacturers investment credit forcleanrooms built by IC manufacturers andsemiconductor equipment companies.Figure 2-9 shows depreciation schedules fora fab facility in the U.S.Within the fab area, the photolithographycell is the most expensive (Figure 2-10), asleading-edge steppers and step-and-scanmachines for 0.25um processing are pricedbetween 5- 7 million each. In addition, theinvestment for advanced reticles is risingrapidly (Figure 2-11). Beyond lithographycosts, the next most expensive is diffusionprocesses, followed by etching, thin filmdeposition, and ion implantation. Trendsindicate a long-term increase in number ofCVD, sputtering, and etching tools in the fab,principally driven by an increasing numberof metal layers in advanced logic devices(currently at 5-6 levels for 64-bit MPUs), andthe introduction of chemical mechanical polishing tools for global planarization. Manysources estimate that back-end wafer processing (all processing of films above thesubstrate level) accounts for more than 50percent of overall cost per wafer.FabCleanroomBuilding EquipmentWaferOfficeProcessingand UtilityEquipmentYear 10%62%15173%83%20%10%61%16180%81%20%10%60%Source: Oregon Department of Revenue 1994-1995 ElectronicsTrend and Depreciation Schedules22729Figure 2-9. Depreciation Schedules Projected Appraised Value of Investmentas Percentage of Original Cost2-8INTEGRATED CIRCUIT ENGINEERING CORPORATION

Cost Per WaferImplant12%Thin ce: Microlithography World21070Figure 2-10. Relative Costs of Semiconductor Manufacturing AreasBillions of Dollars1,000Semiconductor Market10010Mask Market10.1197719801985199019952000YearSource: Wafer News/Rose Assoc.22693Figure 2-11. Growing Investment in Reticles and MasksLong-term increases in depreciation andR&D expenditures continually challenge thecost-effectiveness of IC manufacturing. Onemetric used to examine overall cost effectiveness is asset turnover rate. Figure 2-12shows that in the years preceding 1980,every dollar of net fixed assets generatedgreater than 3.00 in sales revenue. By 1987,asset turnover rate had fallen by 50 percent.However, recent trends indicate that assetturnover rates are stabilizing. However, further deterioration in the rate may affect thefinancial future of the industry. Once again,by making facilities and operations morecost effective, margins can be preserved andthe rate of technological advancement cancontinue at its rapid pace. Astoundingly, theaverage employee of a merchant IC manufacturer in the U.S. is supported by 120,000in net fixed assets (Figure 2-13).INTEGRATED CIRCUIT ENGINEERING CORPORATION2-9

Cost Per Wafer4.0Net Fixed Assets/Sales ( )3.53.02.5MeanMedian2.01.51978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995YearSource: SIA22730Figure 2-12. Net Fixed Assets Rise Faster Than Industry Revenues140120 1,000 Per Employee1008060Median4020Mean01978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995YearSource: SIA22731Figure 2-13. Net Fixed Assets Per Employee2-10INTEGRATED CIRCUIT ENGINEERING CORPORATION

Cost Per WaferThe Cost of LaborAs semiconductor fabs become more automated and reliable, labor costs typically represent a smaller portion of total waferprocessing costs. As shown back in Figure 21, total labor costs typically constitute 11.5percent of overall cost per wafer for U.S.firms. Figure 2-14 shows how the total laborrate (including wages, salaries, payroll taxes,etc.) as a percent of sales for U.S. firms hasdropped dramatically over the last severalyears and the divergence between the meanand median lines indicates that larger firmsspend much less on labor than smaller ICmanufacturers, which is expected. Figure 215 gives a sampling of salaries and wagesearned by different individuals working inor around the fab.By 1996, labor rate differences between theU.S. and Japan had diminished due tochanging standards in Japan and the changing value of the yen (Figure 2-16). Thesemiconductor industry has become a trulyglobal industry with fabs now emerging inall regions of the world. Regions that haverecently attracted fabs include China,Malaysia, Thailand, India, and EasternEurope. These countries offer the labor costadvantages that Japan once enjoyed overthe U.S. It comes as no surprise that theseregions, home to many assembly houses,are now being used for wafer processing.Such developing regions offer enormousgrowth potential, as evidenced in thegrowth of exports in developing regions relative to export growth in developed regions(Figure 2-17).50Percent of Sales Revenues45Median4035Mean3025201978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994Year*Includes wages, salaries, retirement expenses, incentive compensation, payroll taxes**North American firms onlySource: SIA21072Figure 2-14. Total Labor Expenses* as a Percent of Sales Revenues**INTEGRATED CIRCUIT ENGINEERING CORPORATION2-11

Cost Per tor (Dollars/Hour)Operator Wafer Fab I6.309.98Operator Wafer Fab II7.2410.55Operator Wafer Fab III8.2412.69Semiconductor Specialist9.4914.78Semiconductor Line Mech.13.7219.72Process Engineer I30.847.5Process Engineer II35.856.1Process Engineer III44.368.7Process Technician20.331.4Sr. Process Technician25.538.7QA Technician I18.227.1QA Technician II20.630.9QA Technician III24.336.7QA Engineer33.851.0Process Development Manager53.681.6QA Manager47.474.4MIS Manager49.678.4R & D Manager60.194.8HR Manager43.668.2Compensation Manager47.471.6Emp. Relations Manager50.480.8Gen. Accounting Manager43.468.2Facilities Manager43.268.6Office Manager31.047.4Production Manager41.164.7Test Engineer34.552.8CAD Operator I20.530.5Accounting Clerk utive Secretary24.936.9Administrative Assistant24.837.3Data Entry Operator17.024.3Semiconductor (Thousands of Dollars/Year)Elec. Management (Thousands of Dollars/Year)Other Technical (Thousands of Dollars/Year)Clerical (Thousands of Dollars/Year)Definitions – Minimum 50th Percentile: The minimum salary range whichis higher than 50% of all minimum ranges.Maximum Average: The average of the maximumsalary ranges reported.Source: American Electronics Assoc.21076Figure 2-15. Typical Industry Salary Ranges in U.S., West Coast2-12INTEGRATED CIRCUIT ENGINEERING CORPORATION

Cost Per Wafer1996U.S. WAFER FABDIRECT LABOR RATECOSTFACTORJAPANESE WAFER FAB DIRECTLABOR RATE1985 - 1986*1996** 11.80 5.50 11.2135%40%40%TOTAL 15.93 7.70 15.69LABOR COST PERWAFER TO PROBE(1.5 HOURS) 23.90 11.55 23.54HOURLY RATEFRINGE RATE* 205 1.00**108 1.0012030JSource: ICEFigure 2-16. U.S. and Japanese 1995 IC Facility Direct Labor Costs220217.1200Percentage of conomiesSource: Wall Street Journal/DRI/McGraw HillWorldIndustrializedEconomies22701Figure 2-17. Real Growth of Exports in the World, 1995-1996INTEGRATED CIRCUIT ENGINEERING CORPORATION2-13

Cost Per WaferWorldwide, the semiconductor industryemploys roughly between 750,000 and a million people (Figure 2-18). Of these, approximately 260,000 are employed by NorthAmerican merchant semiconductor manufacturers. Figure 2-19 shows the cyclical patterns in North American on-shore andoff-shore employment levels in response tochanging market condition. As shown,employment levels have increased significantly between 1992 and 1995, despite continual advances in labor productivity. In1995, approximately 70 percent of the NorthAmerican wages were disbursed to employees in North America, and the off-shoreemployee earns approximately one-third thesalary of the employee based in NorthAmerica, reflecting the semi-skilled labor atoff-shore assembly operations as opposed tothe base of highly-skilled and professionalworkers at North American facilities. Thispay differential is narrowing slowly (Figure2-20) as off-shore wages steadily increase.1,2001,100Employees 2000*Year* ProjectedSource: Electronic Business Today22689Device Cost ModelingSeveral years ago ICE developed a simplifiedcost model to examine manufacturing costs.The model estimate a company's grossmargin and revenues for a given devicebased on the ASP for the devices at the time,and a calculation of device factory cost basedon design rules, type of device, equipmentcost, wafer size used, defect density estimates, etc. Among these assumptions, defectdensity is the most critical. Through fabbenchmarking studies and cost modeling,ICE developed the wafer cost estimatesshown in Figure 2-21.Figures 2-22 and 2-23 show cost modelresults for a Pentium microprocessor and16M and 64M DRAM devices in first quarter1997. As shown, the advanced-generationPentium device yields a significant grossmargin as little competition exists in thismarketplace. As the advanced-generationPentiums mature and are replaced by thePentium Pro device, Intel will continue tolower the price of this processor more dramatically and improve yields more quicklyto preserve margins.The margins on DRAM devices, however,have dramatically declined in the past year,forcing important changes in the 16MDRAM market and the adoption of 64Mtechnology. At least some DRAM manufacturers are accelerating their transition to 64Mproduction due to the slim profit margins of16M devices, as illustrated in Figure 2-23. Atthe same time, manufacturers are rapidlyshrinking the die size of 16M devices fromtypical levels of 80mm2 to as small as 60mm2to preserve yields and margins.Figure 2-18. Worldwide SemiconductorEmployment2-14INTEGRATED CIRCUIT ENGINEERING CORPORATION

Cost Per Wafer150North AmericaOffshore1401,000 Employees130120110100901978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995YearSource: SIA22732Figure 2-19. North America and Offshore Employment Levels70Annual GrowthTrend 10.8%60 1,000 Per Employee50North American4030Worldwide Average2010Offshore01978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995YearSource: SIA22733Figure 2-20. Labor Expenses Per EmployeeINTEGRATED CIRCUIT ENGINEERING CORPORATION2-15

Cost Per WaferProcess TechnologyFeatureSize (µm)WaferSize (mm)CMOS14-16 MasksAdvancedCMOS18-20 MasksAdvancedBiCMOS22 MasksBipolar8-10 MasksBipolar14-16 MasksAdvancedBipolar22 / ource: ICEFigure 2-21. Whole Wafer Cost Before Probe ( )BiCMOS MPU (0.35µ)Tested Wafer Cost 1,890 (200mm epi wafer)Die Size135,000 sq mils (90mm2)Total Dice AvailableProbe YieldNumber Of Good DicePackage Cost29237% (at 1.2 defects/cm 2 )108 25.75 (296-pin CPGA)Assembly Yield99%Final Test Cost 35.00Final Test YieldFactory CostASP (1,000)Approx. Revenue/Wafer Start70% 112.41 350 26,195Revenue/Sq In. Started 542Gross Margin68%Source: ICE14448GFigure 2-22. Pentium (166MHz P54CS) Cost Analysis (3Q96)DRAM, MPU and ASIC ManufacturingCostsDRAM device sector. In addition, the manufacturing technology using multilevel metalization designs of 5 layers or more is drivenby needs of the microprocessor supplier. Theindustry therefore has two very strong segments, DRAMs and microprocessors, drivingthe designs of process equipment, facilities,automation and factory management.The semiconductor industry has traditionally been driven by the needs of the DRAMmanufacturers because these companies arethe single largest consumers of semiconductor equipment and materials, and becauseDRAM devices, until recently, were the technology drivers. In recent years, microprocessors have become the technology driver asIntel has speeded its transitions to smallerfeature sizes faster than the transitions in theDRAM manufacturers produce ICs in highvolume, thereby driving the development ofequipment that delivers the highest throughput possible, while meeting processing2-16INTEGRATED CIRCUIT ENGINEERING CORPORATION

Cost Per Waferrequirements that vary little within a givenfacility. For instance, a fab may be producing1M DRAMs and 4M DRAMs, while runningpilot line production and design of 16M and64M DRAMs, respectively. In addition, different versions of the same generation maybe produced, for instance, for 3.3V and 5.0Voperation, or 4x4 and 1x16 bit cell configurations. Due to the small differences in processing requirements for these devices,generally two generations of equipment arefound in DRAM fabs. High-volume production also means that production lots of 24wafers at a time are almost always run, andengineers have the luxury of dedicatingprocess tools to certain processes, therebyimproving processing results.At the other extreme are ASIC manufacturers. ASIC production means that lot sizesvary from one to twenty-four wafers; everylot has a different mask set; wafers are produced in small volume; the product line contains several generations of equipment; andthe fab must be constructed to be veryresponsive to changes. ASICs are also moredifficult to analyze than memory devices.Memories are highly testable structures andyield learning is only performed once for aproduct that will be manufactured for 8-10years. ROI typically takes 2-3 years for eachnew generation of DRAMs. For ASICs, thereis very little time for yield learning and reliability studies. The delivered design must be"fool-proof," negating the need for failureanalysis and yield analysis. Acceptable yieldfrom the time manufacturing is started is aprerequisite for ROI over a few months, andthe guarantee that delivery dates are met.For these reasons, simulation plays a largerole in device and process development forASICs, whereas process simulation for memories is not traditionally performed, andpilot runs suffice. In general, ASIC manufacturing also drives the development of computer aided design and factory controlsoftware, and packaging technology, due tolarger chip sizes of varying dimensions.16M DRAM (0.35µ)Tested Wafer CostDie Size 1,180 (200mm) 1,485 (200mm)84,000 sq mils (54mm2)232,500 sq mils (150mm2)47616280% (at 0.5 defects/cm2)40% (at 0.7 defects/cm2)Total Dice AvailableProbe Yield64M DRAM (0.35µ)Number Of Good DicePackage Cost38065 0.40 0.50Assembly Yield99%99%Final Test Cost 0.60 1.20Final Test Yield95%85%Factory Cost 4.36 29.15ASP 7.75 55.00Approx. Revenue/Wafer Start 2,770 3,008Revenue/Sq In. Started 55 60Gross Margin44%47%16912GSource: ICEFigure 2-23. 16M and 64M DRAM Cost AnalysisINTEGRATED CIRCUIT ENGINEERING CORPORATION2-17

Cost Per WaferFigure 2-24 shows further differencesbetween DRAM and ASIC manufacturing.The high-volume DRAM manufacturinglines suffer little from reconfiguration andcapacity additions relative to ASIC fabs. Thecost benefits due to automated scheduling,and wafer and mask tracking for ASICs outweigh the same benefits to the DRAM manufacturer. However, too much automationcan inhibit flexibility. In addition, equipment reliability, mean time to repair (MTTR),and the importance of being able to quicklymake real-time process changes, are muchmore important to the ASIC manufacturer.Development equipment must be extremelycomparable to manufacturing equipment asyield ramp-up for ASICs must be minimized.Other Key Cost TrendsIn addition to product yield, cycle time, laborcosts, and equipment productivity, important components in cost per wafer includethe cost of equipment maintenance, testwafers, and consumables. Although discussing every cost components in detail isbeyond the scope of this book, some highlights provides insight into their importance: Contracted maintenance costs varybetween nothing ( 0) for the first twoyears, to up to 400,000 per tool per year,depending on the equipment supplier andterms of the contract. Equipment installation, including toolhook-up and the running of test wafers tofull qualification, typically adds 35 percentto the price of the tool.As far as manufacturing cycle time and workin process (WIP) are concerned, the fab with agreater number of different products beingprocessed at once (greater variability) willreach higher levels of WIP and longer cycletimes, faster (Figure 2-25). Achieving lowcycle time in the presence of variabilityrequires either flexible equipment or idle time.IssuesModularityBenefits Due to ComputerIntegrated ManufacturingImportant EquipmentCharacteristics The cost of cleaning gases for single-wafertools is significantly higher than for batchtools. In-situ cleaning procedures also contribute significantly to tool downtime.MeasureASICDRAMCost of ReconfigurationHighLowCost of Capacity AdditionsHighMediumAutomated DownloadingHighLowWafer/Mask iumHighMediumMediumHighReal Time Process ChangeHighMediumDev. Eqpt. Mfg. Eqpt.HighMediumMTTRDefect FreeSource: Motorola19775Figure 2-24. Relative Fab Characteristics2-18INTEGRATED CIRCUIT ENGINEERING CORPORATION

Cost Per Wafer Test wafer cost rises dramatically at the200mm level as manufacturers use primepolished wafers, rather than reclaimedwafers, for process monitoring. Studies indicate that some fabs are spending 1 million or more a month on testwafers, which does not include the cost oflost productivity when tools are runningthese wafers[3].References1. J. Smits, et.al., ÒLogistics in Fab Design,ÓFuture Fab International, p. 101.2. 1978-1995 Industry

Cost per wafer at the fab level can be simply computed using the total cost of manufactur-ing divided by the total number of yielded wafers produced. Cost per wafer at the equipment level is typically computed Òfrom the ground-upÓ using the cost of equipment depreciation, cost of direct labor, mainte-nance

Smithsonian STEAM Readers Aligned to Next Generation Science Standards Grades 3–5 Teacher Created Materials www.tcmpub.com (800) 858-7339 B3418 2019 Smithsonian Institution. The name “Smithsonian” and the Smithsonian logo are registered trademarks owned by the Smithsonian Institution.

The CMOS Process - photolithography (1) Silicon Wafer Silicon Wafer SiO 2 1μm Silicon Wafer photoresist (a) Bare silicon wafer (b) Grow Oxide layer (c) Spin on photoresist Lecture 3 - 4 The CMOS Process - photolithography (2) Silicon Wafer (d) Expose resist to UV light through a MASK Silicon Wafer (e) Remove unexposed resist Silicon Wafer

The wafer alignment system demonstrated in this paper consists of a three-pin passive wafer alignment stage, a voice coil actuated nesting force applicator, a three degrees-of-freedom (DOFs) wafer handling robot, and a wafer cas- . focusing of a

The problem is that most traditional 300mm wafer fabs are highly complex (with hundreds of processing steps), and have high throughput requirements (over 20,000 wafer starts per month). As a result, the existing AMHS technology operating in a 300mm wafer fab is fac-ing the following challenges: 1. To reduce wafer cycle time average and standard

grinding wheel. The diamond surface of this grinding wheel is shaped exactly opposite to the desired end result shape of the wafer edge. The wafer is either fed into the diamond wheel, or the diamond wheel is fed into the wafer, depending upon the machine design. This type of machine

Summary 29 Easily obtained uniform and high contact force 300mm wafer 576kgF, max 120K pin 450mm wafer 1,297kgF, max 260K pin *‐80kPa, 5gf/pin Because pressure is uniformly distributed over the tester and the wafer sides, a high stiffness structure is not required for prober and card Realized full wafer contact by VPCS Existing MEMS probe

notch [4] in the wafer and plate, respectively, in the bonding process. The system can measure the amount of change in the detected edge and align the wafer and plate. Conventionally, wafer alignment is performed based on the flat surface of the wafer and the notch of the ceramic plate. A method using

ADVANCED ENGINEERING MATHEMATICS By ERWIN KREYSZIG 9TH EDITION This is Downloaded From www.mechanical.tk Visit www.mechanical.tk For More Solution Manuals Hand Books And Much Much More. INSTRUCTOR’S MANUAL FOR ADVANCED ENGINEERING MATHEMATICS imfm.qxd 9/15/05 12:06 PM Page i. imfm.qxd 9/15/05 12:06 PM Page ii. INSTRUCTOR’S MANUAL FOR ADVANCED ENGINEERING MATHEMATICS NINTH EDITION ERWIN .