Suspend-to-RAM Implementation On Freescale 74xx Without

Suspend-to-RAMimplementation on Freescale74xx without PMU4/18/2007Fujihito NumanoCorporate Software Engineering CenterCopyright 2007, Toshiba Corporation.

Agenda – Goals and Backgrounds1. Target Board2. Goals3. Backgrounds– Freescale 74xx programmable power mode– PMU (Power Management Unit)4. Idle power management5. Suspend to RAM––––Overviewenter state()Device Power Managementpm ops functions6. Performance7. Our next challengesSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.2

1. Target BoardTOSHIBA TEC Corporation development boardCPU Freescale 74xxwithout PMUSome devices need to be resume triggerNo non-volatile memorySuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.3

2. GoalsRequirementThe system automatically enters in the low-power “sleep” modeafter a period of inactivity.Status – Implemented a test version– Go to suspend to RAM after a period of inactivity– Reduce power consumption by more than 50%– Resume triggered by the specific device access.Points– Suspend to RAM with 74xx power saving “sleep” mode– Device control without “PMU”– Simple & compact implementationSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.4

3. Backgrounds The system enters in the low-power “sleep” modeautomatically after a period of inactivity to reducepower consumption. The system returns to the normal “working” modeimmediately if needed. The boot up time is so long that ,power off and system shutdown cannot be usedSystem suspend & resume should be used.Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.5

3. Backgrounds No non-volatile memory Hibernation function cannot be supported“Suspend to RAM”, “Idle power management”, and“Device power management (Device on and off control)” functions.are effective. The target CPU is Freescale 74xx It needs to support programmable power modeand we plan how to implement suspend to RAM by using it. No external H/W, such as PMU (Power ManagementUnit), supports to control power status The kernel itself should control power statusand especially control resume trigger devices.Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.6

Freescale 74xx power saving mode2 power saving modes are available to the system,Nap mode and Sleep modeNap modeInstruction fetching is halted.The clocks for time base, decrementer remain running.So the CPU is soon returned to the normal (RUN) modeby the “decrementer” timer interruption The system cannot keep the “power saving mode (Nap)”.Nap mode should not be applied to suspend to RAMbut Idle power management.Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.7

Freescale 74xx power saving modeSleep modePower consumption is further reduced by disabling bus snooping.All internal functional units are disabled.Internal exception, such as timer interrupt ,does not occur.So the system does not return to normal mode by itself. The system can keep sleep “power saving” mode.It is appropriate for suspend to RAMDisabling bus snooping The system needs to flush TLB and cache on resume.Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.8

PMU – The Power Management UnitThe Power Management Unit (PMU) is a microcontrollerthat governs power functions for Apple computers.And is responsible for coordinating following powermanagement functions.– Monitoring power connections and battery charges– Charging batteries when necessary– Controlling power to other integrated circuits– Shutting down unnecessary components when they are left idle– Controlling sleep and power functions (on and off)( from Wikipedia, the free encyclopedia)Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.9

Without PMU supportWithout PMU , the kernel needs to do somepower management functions by itself.– Controlling power to other integrated circuits– Shutting down unnecessary system componentswhen they are left idle– Controlling sleep and power functions (on and off)(In the target, the resume trigger devices are controlled in particular)Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.10

Agenda - Implementations and Performance1. Target2. Goals3. Backgrounds– Freescale 74XX programmable power mode– PMU (Power Management Unit)4. Idle power management5. Suspend to RAM––––Overviewenter state()Device Power Managementpm ops functions6. Performance7. Our next challengesSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.11

4. Idle power management The idle power management for 74xx has beenalready implemented in the power PC kernel When the kernel starts, the idle process is launched.It is set to the lowest priority by the process scheduler . If “/proc/sys/kernel/powersave-nap” is set to 1,the idle process tries to set the CPU to NAP mode.Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.12

5. Suspend to RAM implementation - Overview Implementations for 74xx sleep mode– Save and restore the processor contexts– Timer , TLB and cache flush– The resume exception handler Device control without “PMU”– The resume trigger devices are controlled in particular. Simple & compact implementation– All functions dependent on 74xx are wrapped on pm ops function table .– All functions independent on the CPU architecture can be used without anychanges , such as enter state() and device power management functions.Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.13

enter state()All suspend to RAM implementations are included inenter state() function.Applications and following suspend command also call itindirectly.#echo –n mem /sys/power/stateIt is based on preprocessing, main and post processingfunctions.suspend prepare()suspend enter()suspend finish()Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.14

enter state()The functions dependent on 74xx are wrapped on thepm ops function table.All implements independent on the CPU architecturecan be applied to the target system without any change. Process control Console control Device power managementSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.15

enter state()enter state()suspend prepare()pm prepare console()disable nonboot cpus()freeze processes()nr free pages()pm ops- prepare()suspend console()device suspend()suspend enter()device power down()pm ops- enter()device power up()suspend finish()device resume()resume console()thaw processes()enable nonboot cpus()pm ops- finish()pm restore console() exchange the virtual console for the one of suspend only Stop other CPUs ( for multi processor ) Freeze processes check and allocate memories for suspend preprocessing for the suspend dependent on 74xx suspend the console output suspend the devices suspend devices which fail to suspend in device suspend() functionor others main routines dependent on 74xx. The system suspend here resume devices resume devices entried in the dpm off table resume the console output resume processes restart other CPUs( for multi processor ) post-processing for the suspend dependent on 74xx restore the virtual consoleSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.16

Device Power Management The kernel can control device power state by “device xx” functions. “device register” function entries the device in the “dpm active” list atthe initialization of the driver. All devices in the list can be controlled bythe kernel. On suspending the system, enter state() calls device suspend() anddevice power down().The devices are set to device power down or device off state. On resuming the system, enter state() function callsdevice power up() and device resume() function.The devices are restored to device power on state.Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.17

Device Power Management functionsenter state()suspend prepare():pm ops- prepare():device suspend()suspend enter()device power down() suspend the devices suspend devices which fail to suspend in device suspend()or devices not entried in the dpm active tablepm ops- enter()device power up()suspend finish()device resume():pm ops- finish(): resume devices resume devices entried in the dpm off tableSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.18

Device Power Management for resume trigger devices The resume trigger devices are controlled in particular. While the system suspends, their exception handlers areexchanged for the resume exception handlers(for 74xx sleep mode).ExampleResume Trigger DeviceGeneral DeviceLAN (supports wake-up on LAN)HDDLCDPower buttonLCD “rid” buttonInput deviceResume TriggerYesNoControl functionpm ops functionsdevice xx()(dependent on 74xx)(independent on the CPUarchitecture)Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.19

Power Management for resume trigger deviceenter state()suspend prepare():pm ops- prepare():device suspend()The deviceexception handlerexchangesuspend enter():pm ops- enter(){suspendreturn}:suspend finish()device resume():pm ops- finish():exchangeThe resumeexception handlerresume74xx sleep modeThe deviceexception handlerSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.20

pm ops function table “pm ops” function table can wrap functions dependent on 74xx.All functions independent on the CPU architecture can be usedwithout any changes ,such as enter state() and device power management functions. Our reference comes from the implementations in the x86 kernel.implemented mainly ACPI BIOS processing. The codes, preprocessing , main routines and post-processing, are setin the table as follows. They are called from enter state() function./drivers/power/main.cstatic struct pm ops acpi pm ops {.prepare acpi pm prepare,.enter acpi pm enter,.finish acpi pm finish,};Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.21

pm ops- prepare()enter state()suspend prepare():pm ops- prepare():The deviceexception handlerexchangeThe resumeexception handlerdevice suspend()suspend enter():pm ops- enter(){suspendresume74xx sleep modereturn}:suspend finish()device resume():pm ops- finish():exchangeThe deviceexception handlerSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.22

pm ops- prepare()The preprocessing dependent on 74xxis wrapped in pm ops - prepare() function.1. Interrupt disabled by the exception of resume trigger devices.Usually the interrupts are used for their device controls.Disabled for the followings2. Exchange the exception handlers for the exception handlers forresume only.The resume exception handler is the start point where the 74XX systemresume from the sleep mode. Our reference comes from the following pm ops- prepare()implementations in the x86 kernel.– Control resume trigger devices and their device state– Prepare resume vectorsSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.23

pm ops- enter(), the resume exception handlerenter state()suspend prepare():pm ops- prepare():device suspend()The deviceexception handlerexchangesuspend enter():pm ops- enter(){suspendreturn}:suspend finish()device resume():pm ops- finish():exchangeThe resumeexception handlerresume74xx sleep modeThe deviceexception handlerSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.24

pm ops- enter()The suspend main routine dependent on the CPU architecture.is wrapped in pm ops - enter() function.1.Interrupt enabled by the exception of resume trigger devices (resumeexception handlers).2.3.4.Save the processor contextsDestroy timer and cacheGo to Freescale 74XX sleep mode(The system goes to suspend)5.6.Returned from the resume exception handler.Interrupt disabled by the exception of resume factor devices (resumeexception handlers). Our reference comes from the following pm ops- enter() implemented in the x86 kernel.– Save the processor contexts– Flush cacheSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.25

The exception handler for resume only The resume starts from the resume exception handler.It is set in pm ops- prepare(),and set off in pm ops- finish(). Followings is the flow of the handler.1. Restore the CPU contexts2. Validate timer and cache3. Flush cache and TLB4. Reassemble MMU5. Finish (and return to pm ops- enter() function)Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.26

pm ops- finish()enter state()suspend prepare():pm ops- prepare():device suspend()The deviceexception handlerexchangesuspend enter():pm ops- enter(){suspendreturn}:suspend finish()device resume():pm ops- finish():exchangeThe resumeexception handlerresume74xx sleep modeThe deviceexception handlerSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.27

pm ops- finish()The postprocessing dependent on the CPU architecture iswrapped in pm ops - prepare() function.1. Restore the normal exception handler of the resumetrigger devices from the resume exception handlers2. Interrupt enabledSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.28

6. Performance We implemented test version. And succeed to reduce power consumptionby more than 50%.Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.29

7. Our next challenges Measureing the resume speed and optimizing thekernel if needed. Longer persistence of Idle ( Nap mode )with tickless kernel function. Hibernation function supports for the next targetwith non-volatile memorySuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.30

AcknowledgementTOSHIBA Corporate Software Engineering CenterHiroshi NozuweTsutomu OwaMasahiro YamadaFujihito NumanoTOSHIBA TEC Corporation membersTOSHIBA Information Systems membersSuspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.31

Suspend-to-RAM implementation on freescale 74xx without PMUCopyright 2007, Toshiba Corporation.32

device_power_down() suspend devices which fail to suspend in device_suspend() function or others pm_ops- enter() main routines dependent on 74xx. The system suspend here device_power_up() resume devices suspend_finish() device_resume() resume devices entried in the dpm_off table

Suspend/Resume Is Expensive Slow suspend/resume is long known for desktop/server Suspend/resume mostly slowed down by SATA and USB devices These machines suspend/resume only occasionally Much worse on mobile/IoT due to short-lived tasks Suspend/resume takes 500 ms on Samsung Note4 Smartphone

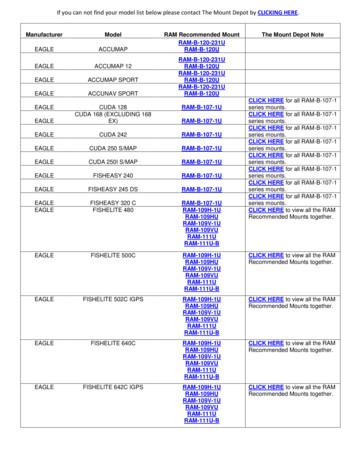

FISHFINDER 340C : RAM-101-G2U RAM-B-101-G2U . RAM-101-G2U most popular. Manufacturer Model RAM Recommended Mount The Mount Depot Note . GARMIN FISHFINDER 400C . RAM-101-G2U RAM-B-101-G2U . RAM-101-G2U most popular. GARMIN FISHFINDER 80 . RAM-101-G2U RAM-B-101-G2U . RAM-101-

RAM Combat, RAM Desert Eagle Ages 18 12/06 P000524 Read this owner’s manual completely. This marker is not a toy. Treat it with the same respect you would a firearm. Always carefully follow the safety instructions found in this owner’s manual and keep this manual in a safe place for future use. RAM Combat RAM X50 RAM Desert Eagle

Chapter 5: Ram Stavaraj, Ram Ashtaks & Ram Raksha Stotra: Page: 411-480 (5.1) Ram Stavaraj Stotra—Page: 411 (5.2) Ram Ashtak Stotra—Page: 452 (5.3) Raghunaath Ashtak Stotra—Page: 456 (5.4) Sita Ram Ashtak Stotra—Page: 461 (5.5) Ram Raksha Stotra—Page: 468 Chapter 6: Lord Ram’s Mantras appearing in the ‘Upanishads’: Page: 481-551

Raksha karo, raksha karo, Sain Kapish Bhavtari Shri Ram Vandana Param Purush Aadi Narayan, Jan-hit-kari Ram Muni-man ranjan, Bbhav-bhay bhanjan, Asur Sanhari Ram Jagpita Mata, Survar Data, Bhagat bhay-hari Ram Kaljug Sain roop dharaye, Rachna Tari Ram Param Vidhata, Bhavjal Trata, Charan-vari Ram Jag mein aayo, Anand chhayo, Santan dukhhari Ram

2016-18 Ram 1500 Rebel, 2018 Ram 1500, 2019 Ram 1500 Classic (Metal Bumpers) (Inc. EcoDiesel); 2016-18 Ram 1500 Bighorn/aramie/aramie onghorn (Chrome Bumpers) Installation Instructions. 405-0571 Rev D Page 2 of 6 11/8/18. . 2016 DODGE RAM 1500 REBEL EC # 4826; PROJECT # R4226; GVWR: 6800 lbs 35" BETWEEN TAB CENTERS DATE OF MFG: 10/15

How to force Dark Suspend/Resume Run-time suspend display before system-suspend: xset -display :0 dpms force off sleep 2 sudo analyze_suspend.py Display will not be resumed upon system-resume, but availability is platfor

N. Suttle 2010. Mineral Nutrition of Livestock, 4th Edition (N. Suttle) 1 1 The Requirement for Minerals Early Discoveries All animal and plant tissues contain widely vary-ing amounts and proportions of mineral ele-ments, which largely remain as oxides, carbonates, phosphates and sulfates in the ash after ignition of organic matter. In the .