Constructive Computer Architecture Tutorial 4: SMIPS On

Constructive Computer ArchitectureTutorial 4:SMIPS on FPGAAndy Wright6.S195 TAOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-1

IntroductionField programmable gate arrays (FPGAs) arechips filled with fine grained configurablehardware Can think of it as logic gates that you canconnect togetherThey are a prototyping tool in ASIC designflowThey are the end-target for many designs Low volume custom hardwareThey are also very useful for simulationLater labs will use FPGA tools to compileBluespec code for an FPGAOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-2

BSV Design FlowBSV sourceBluespec CompilerVerilog RTLBluespecSimulatorCycleAccurateVCD outputOctober 7, 2013Xilinx 6.s195Xilinx XSTSynthesisGatesT04-3

Original Test Bench SetupmkTestBenchStartmkProchostToCpuRuncpuToHost- This setup isn’t suited to test a design on an FPGA.- None of the output from the test can be seen by the usersince all commands are ignored during FPGA synthesisOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-4

SceMi InfrastructuremkBridgespecializedSceMiinterfaceto t- The SceMi infrastructure sets up a way to access interfacemethods of a DUT through a common connection to theoutside worldOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-5

Sample Scemi InterfacesTCP – for bsim simulations ofscemi connectionXUPV5Image of XUPV5 from Xilinx ober 7, 2013http://csg.csail.mit.edu/6.s195T04-6

Scemi using TCPHost ComputerTestbenchwritten in C October 7, 2013TCPBluespec DUTsimulation inBSIMhttp://csg.csail.mit.edu/6.s195T04-7

Scemi using XUPV5Host ComputerXUPV5FPGATestbenchwritten in C PCIEBluespec DUTon FPGASame testbench fromthe TCP exampleOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-8

TCP vs XUPV5TCP Can see output from commands Don’t have to wait for FPGA compilation- Not testing hardwareXUPV5 Actually running Bluespec code on FPGAMore things can go wrongHarder to DebugFaster simulation!Filter:SMIPS: 867329 cyclesCPU sim: 10 secondsFPGA: 25 msOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-9

Debugging on FPGAYou can’t see the effects of: display Used to give basic debug information from processorin simulation fwrite Used to give essential output from the simulation finish Used to stop the processor early on errorAll output seen by the user must passthrough the SceMi Interface October 7, 2013The current setup only allows for printstatements from SMIPS programs andPASSED/FAILED outputAn improved interface could give more feedbackhttp://csg.csail.mit.edu/6.s195T04-10

Old Processor Interfaceinterface Proc;method ActionValue#(.) cpuToHost;method Action hostToCpu(Addr startpc);endinterfaceOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-11

Old C Test BenchLook at Run.cppLook at function that prints to stderrfrom cpuToHostOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-12

Interface ImprovementsGDB Inspired More program flow control: start, step, stop read PC, write PC Read processor state: Read registers, read memory Read profiling stats cycle count, instruction countOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-13

Debug Processor Interfaceinterface ProcDebug;method ActionValue#(.) cpuToHost;method Action start(Bool ignore);method Action step(Data steps);method Action stop(Bool ignore);method Addr read pc;method Action write pc(Addr d);method Action req read rfile(Bit#(5) r);method ActionValue#(Data) resp read rfile();method ActionValue#(Data) read mem32(Addr addr);method Addr read cycle;method Addr read inst;endinterfaceOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-14

New 1cyc.bsvLook at 1cyc.bsvAlso includes modified coprocessorOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-15

New SceMiLayer.bsvLook at SceMiLayer.bsvOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-16

New C Test BenchLook at Run-debug.cppLook at the new functions includedfor debuggingOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-17

Output from C TestBenchLook at output.txtOctober 7, 2013http://csg.csail.mit.edu/6.s195T04-18

SMIPS Debugger ProgramGive user interactive control overprocessor on FPGA October 7, 2013User can type start, step n ,stop, and other similar commandsThey can also choose to get theentire processor state when theprocessor is stoppedThis is still a work in progresshttp://csg.csail.mit.edu/6.s195T04-19

Adding breakpoints toSMIPSThe user needs to be able to specify a PCto stop at New interface method to write breakpoint toprocessorThe processor needs to be able to storebreakpoints The processor needs a breakpoint registerThe processor needs to stop when thatPC has been reached October 7, 2013Coprocessor needs to monitor PC andchange processor state accordinglyhttp://csg.csail.mit.edu/6.s195T04-20

SceMi simulation bugs?Look at bugs.txtCycle count and instruction count don’tmatch for print and filter when running1cyc.bsvThis is not a bug, the coprocessor fifo isgetting filled because the C test benchis slower at dequeuing from the fifo thanthe BSV test bench. The filled coprocessorfifo is forcing the processor to stall.October 7, 2013http://csg.csail.mit.edu/6.s195T04-21

ConclusionFPGA simulation is harder, butSceMi’s interfaces make it easier.The TCP SceMi interface allows fortesting software written for FPGAsimulation without using the FPGA.More advanced debuggingtechniques can be used by addingto the processor interface.October 7, 2013http://csg.csail.mit.edu/6.s195T04-22

Tutorial 4: SMIPS on FPGA Andy Wright 6.S195 TA . Can think of it as logic gates that you can connect together They are a prototyping tool in ASIC design . - This setup isn’t suited to test a design on an FPGA. -

What is Computer Architecture? “Computer Architecture is the science and art of selecting and interconnecting hardware components to create computers that meet functional, performance and cost goals.” - WWW Computer Architecture Page An analogy to architecture of File Size: 1MBPage Count: 12Explore further(PDF) Lecture Notes on Computer Architecturewww.researchgate.netComputer Architecture - an overview ScienceDirect Topicswww.sciencedirect.comWhat is Computer Architecture? - Definition from Techopediawww.techopedia.com1. An Introduction to Computer Architecture - Designing .www.oreilly.comWhat is Computer Architecture? - University of Washingtoncourses.cs.washington.eduRecommended to you b

Dec 31, 2012 · Computer Architecture: A Constructive Approach Using Executable and Synthesizable Speci cations . This book is intended as an introductory course in Computer Architecture (or Computer Organization, or Computer Engineering) for undergraduate students who have had a basic . (the Fith

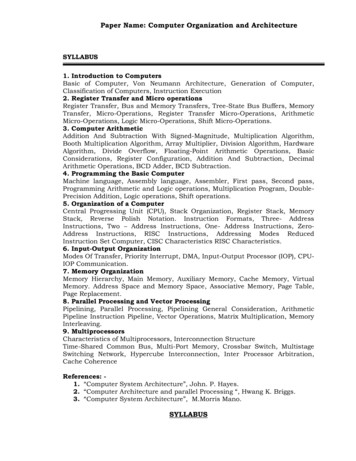

Paper Name: Computer Organization and Architecture SYLLABUS 1. Introduction to Computers Basic of Computer, Von Neumann Architecture, Generation of Computer, . “Computer System Architecture”, John. P. Hayes. 2. “Computer Architecture and parallel Processing “, Hwang K. Briggs. 3. “Computer System Architecture”, M.Morris Mano.

Constructive Computer Architecture Arvind Computer Science & Artificial Intelligence Lab Massachusetts Institute of Technology 6.175: L01 -September 6, 2017

Brief History (Impredicative) Type Theory. 1971 Per Martin-Löf,A theory of Types. (Predicative) Type Theory as Constructive Set Theory. 1979 Per Martin-Löf,Constructive Mathematics and Computer Programming . 1984 Per Martin-Löf,Intuitionistic Type Theory. (Predi

Tutorial Process The AVID tutorial process has been divided into three partsÑ before the tutorial, during the tutorial and after the tutorial. These three parts provide a framework for the 10 steps that need to take place to create effective, rigorous and collaborative tutorials. Read and note the key components of each step of the tutorial .

Tutorial Process The AVID tutorial process has been divided into three partsÑ before the tutorial, during the tutorial and after the tutorial. These three parts provide a framework for the 10 steps that need to take place to create effective, rigorous and collaborative tutorials. Read and note the key components of each step of the tutorial .

Tutorial 1: Basic Concepts 10 Tutorial 1: Basic Concepts The goal of this tutorial is to provide you with a quick but successful experience creating and streaming a presentation using Wirecast. This tutorial requires that you open the tutorial document in Wirecast. To do this, select Create Document for Tutorial from the Help menu in Wirecast.