Computer Organization And ArChiteCture Designing For Performance - Pearson

Computer Organizationand ArchitectureDesigning for PerformanceEleventh EditionA01 STAL7193 11 SE FM.indd 11/26/18 9:34 AM

A01 STAL7193 11 SE FM.indd 21/26/18 9:34 AM

Computer Organizationand ArchitectureDesigning for PerformanceEleventh EditionWilliam Stallings330 Hudson Street, New York, NY 10013A01 STAL7193 11 SE FM.indd 31/26/18 9:34 AM

Senior Vice President Courseware PortfolioManagement: Marcia J. HortonDirector, Portfolio Management: Engineering, Computer Science & Global Editions: Julian PartridgeExecutive Portfolio Manager: Tracy JohnsonPortfolio Management Assistant: Meghan JacobyManaging Content Producer: Scott DisannoContent Producer: Amanda BrandsR&P Manager: Ben FerriniManufacturing Buyer, Higher Ed, Lake Side Communications, Inc. (LSC): Maura Zaldivar-GarciaInventory Manager: Bruce BoundyField Marketing Manager: Demetrius HallProduct Marketing Manager: Yvonne VannattaMarketing Assistant: Jon BryantCover Designer: Black Horse DesignsCover Art: Shuttersstock/Shimon BarFull-Service Project Management:Kabilan Selvakumar, SPi GlobalPrinter/Binder: LSC Communications, Inc.Copyright 2019, 2016, 2013, 2010, 2006, 2003, 2000 by Pearson Education, Inc., Hoboken, New Jersey 07030.All rights reserved. Manufactured in the United States of America. This publication is protected by copyright andpermissions should be obtained from the publisher prior to any prohibited reproduction, storage in a retrievalsystem, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or likewise.For information regarding permissions, request forms and the appropriate contacts within the Pearson EducationGlobal Rights & Permissions department, please visit http://www.pearsoned.com/permissions/.Many of the designations by manufacturers and seller to distinguish their products are claimed as trademarks.Where those designations appear in this book, and the publisher was aware of a trademark claim, the designationshave been printed in initial caps or all caps.The author and publisher of this book have used their best efforts in preparing this book. These efforts include the development, research, and testing of theories and programs to determine their effectiveness. The author and publishermake no warranty of any kind, expressed or implied, with regard to these programs or the documentation containedin this book. The author and publisher shall not be liable in any event for incidental or consequential damages with, orarising out of, the furnishing, performance, or use of these programs.Library of Congress Cataloging-in-Publication DataNames: Stallings, William, author.Title: Computer organization and architecture : designing for performance / William Stallings.Description: Eleventh edition. Hoboken : Pearson Education, 2019. Includes bibliographical references and index.Identifiers: LCCN 0134997190 ISBN 9780134997193Subjects: LCSH: Computer organization. Computer architecture.Classification: LCC QA76.9.C643 S73 2018 DDC 004.2/2—dc23 LC record available athttps://lccn.loc.gov/1 18ISBN-10: 0-13-499719-0ISBN-13: 978-0-13-499719-3A01 STAL7193 11 SE FM.indd 41/26/18 9:34 AM

To Triciamy loving wife, the kindestand gentlest personA01 STAL7193 11 SE FM.indd 51/26/18 9:34 AM

A01 STAL7193 11 SE FM.indd 61/26/18 9:34 AM

ContentsPreface xiiiAbout the Author xxiiPART ONE INTRODUCTION 1Chapter 1 Basic Concepts and Computer Evolution 11.1Organization and Architecture 21.2Structure and Function 31.3The IAS Computer 111.4Gates, Memory Cells, Chips, and Multichip Modules 171.5The Evolution of the Intel x86 Architecture 231.6Embedded Systems 241.7ARM Architecture 291.8Key Terms, Review Questions, and Problems 34Chapter 2 Performance Concepts 372.1Designing for Performance 382.2Multicore, MICs, and GPGPUs 442.3Two Laws that Provide Insight: Ahmdahl’s Law and Little’s Law 452.4Basic Measures of Computer Performance 482.5Calculating the Mean 512.6Benchmarks and SPEC 592.7Key Terms, Review Questions, and Problems 66PART TWO THE COMPUTER SYSTEM 72Chapter 3 A Top- Level View of Computer Function and Interconnection 723.1Computer Components 733.2Computer Function 753.3Interconnection Structures 903.4Bus Interconnection 923.5 Point- to- Point Interconnect 943.6PCI Express 993.7Key Terms, Review Questions, and Problems 107Chapter 4 The Memory Hierarchy: Locality and Performance 1124.1Principle of Locality 1134.2Characteristics of Memory Systems 1184.3The Memory Hierarchy 1214.4Performance Modeling of a Multilevel Memory Hierarchy 1284.5Key Terms, Review Questions, and Problems 135viiA01 STAL7193 11 SE FM.indd 71/26/18 9:34 AM

viii ContentsChapter 5 Cache Memory 1385.1Cache Memory Principles 1395.2Elements of Cache Design 1435.3Intel x86 Cache Organization 1655.4The IBM z13 Cache Organization 1685.5Cache Performance Models 1695.6Key Terms, Review Questions, and Problems 173Chapter 6 Internal Memory 1776.1Semiconductor Main Memory 1786.2Error Correction 1876.3DDR DRAM 1926.4eDRAM 1976.5Flash Memory 1996.6Newer Nonvolatile Solid-State Memory Technologies 2026.7Key Terms, Review Questions, and Problems 205Chapter 7 External Memory 2107.1Magnetic Disk 2117.2RAID 2217.3Solid State Drives 2317.4 Optical Memory 2347.5Magnetic Tape 2407.6Key Terms, Review Questions, and Problems 242Chapter 8 Input/Output 2458.1External Devices 2478.2I/O Modules 2498.3Programmed I/O 2528.4Interrupt-Driven I/O 2568.5Direct Memory Access 2658.6Direct Cache Access 2718.7I/O Channels and Processors 2788.8External Interconnection Standards 2808.9IBM z13 I/O Structure 2838.10Key Terms, Review Questions, and Problems 287Chapter 9 Operating System Support 2919.1Operating System Overview 2929.2Scheduling 3039.3Memory Management 3099.4Intel x86 Memory Management 3209.5ARM Memory Management 3259.6Key Terms, Review Questions, and Problems 330PART THREE ARITHMETIC AND LOGIC 334Chapter 10 Number Systems 33410.1The Decimal System 335A01 STAL7193 11 SE FM.indd 81/26/18 9:34 AM

Contents ix10.2Positional Number Systems 33610.3The Binary System 33710.4 Converting Between Binary and Decimal 33710.5 Hexadecimal Notation 34010.6Key Terms and Problems 342Chapter 11 Computer Arithmetic 34411.1The Arithmetic and Logic Unit 34511.2Integer Representation 34611.3Integer Arithmetic 35111.4Floating-Point Representation 36611.5Floating-Point Arithmetic 37411.6Key Terms, Review Questions, and Problems 383Chapter 12 Digital Logic 38812.1Boolean Algebra 38912.2Gates 39412.3Combinational Circuits 39612.4Sequential Circuits 41412.5Programmable Logic Devices 42312.6Key Terms and Problems 428PART FOUR INSTRUCTION SETS AND ASSEMBLY LANGUAGE 432Chapter 13 Instruction Sets: Characteristics and Functions 43213.1Machine Instruction Characteristics 43313.2Types of Operands 44013.3Intel x86 and ARM Data Types 44213.4Types of Operations 44513.5Intel x86 and ARM Operation Types 45813.6Key Terms, Review Questions, and Problems 466Appendix 13A Little-, Big-, and Bi-Endian 472Chapter 14 Instruction Sets: Addressing Modes and Formats 47614.1Addressing Modes 47714.2x86 and ARM Addressing Modes 48314.3Instruction Formats 48914.4x86 and ARM Instruction Formats 49714.5Key Terms, Review Questions, and Problems 502Chapter 15 Assembly Language and Related Topics 50615.1Assembly Language Concepts 50715.2Motivation for Assembly Language Programming 51015.3 Assembly Language Elements 51215.4Examples 51815.5Types of Assemblers 52315.6Assemblers 52315.7Loading and Linking 52615.8Key Terms, Review Questions, and Problems 533A01 STAL7193 11 SE FM.indd 91/26/18 9:34 AM

x ContentsPART FIVE THE CENTRAL PROCESSING UNIT 537Chapter 16 Processor Structure and Function 53716.1Processor Organization 53816.2Register Organization 53916.3Instruction Cycle 54516.4Instruction Pipelining 54816.5Processor Organization for Pipelining 56616.6The x86 Processor Family 56816.7The ARM Processor 57516.8Key Terms, Review Questions, and Problems 581Chapter 17 Reduced Instruction Set Computers 58617.1Instruction Execution Characteristics 58817.2The Use of a Large Register File 59317.3Compiler-Based Register Optimization 59817.4Reduced Instruction Set Architecture 60017.5RISC Pipelining 60617.6MIPS R4000 61017.7SPARC 61617.8Processor Organization for Pipelining 62117.9CISC, RISC, and Contemporary Systems 62317.10 Key Terms, Review Questions, and Problems 625Chapter 18 Instruction-Level Parallelism and Superscalar Processors 62918.1Overview 63018.2Design Issues 63718.3Intel Core Microarchitecture 64618.4ARM Cortex-A8 65218.5ARM Cortex-M3 65818.6Key Terms, Review Questions, and Problems 663Chapter 19 Control Unit Operation and Microprogrammed Control 66919.1Micro-operations 67019.2Control of the Processor 67619.3Hardwired Implementation 68619.4Microprogrammed Control 68919.5Key Terms, Review Questions, and Problems 698PART SIX PARALLEL ORGANIZATION 701Chapter 20 Parallel Processing 70120.1 Multiple Processors Organization 70320.2Symmetric Multiprocessors 70520.3Cache Coherence and the MESI Protocol 70920.4Multithreading and Chip Multiprocessors 71820.5Clusters 72320.6Nonuniform Memory Access 72620.7Key Terms, Review Questions, and Problems 730A01 STAL7193 11 SE FM.indd 101/26/18 9:34 AM

Contents xiChapter 21 Multicore Computers 73621.1Hardware Performance Issues 73721.2Software Performance Issues 74021.3Multicore Organization 74521.4Heterogeneous Multicore Organization 74721.5Intel Core i7-5960X 75621.6ARM Cortex-A15 MPCore 75721.7IBM z13 Mainframe 76221.8Key Terms, Review Questions, and Problems 765Appendix ASystem Buses 768A.1Bus Structure 769A.2Multiple-Bus Hierarchies 770A.3Elements of Bus Design 772Appendix BVictim Cache Strategies 777B.1Victim Cache 778B.2Selective Victim Cache 780Appendix CInterleaved Memory 782Appendix DThe International Reference Alphabet 785Appendix EStacks 788E.1Stacks 789E.2Stack Implementation 790E.3Expression Evaluation 791Appendix FRecursive Procedures 795F.1Recursion 796F.2Activation Tree Representation 797F.3Stack Implementation 803F.4Recursion and Iteration 804Appendix GAdditional Instruction Pipeline Topics 807G.1Pipeline Reservation Tables 808G.2Reorder Buffers 815G.3Tomasulo’s Algorithm 818G.4Scoreboarding 822Glossary 826References 835Index 844A01 STAL7193 11 SE FM.indd 111/26/18 9:34 AM

A01 STAL7193 11 SE FM.indd 121/26/18 9:34 AM

PrefaceWHAT’S NEW IN THE ELEVENTH EDITIONSince the tenth edition of this book was published, the field has seen continued innovationsand improvements. In this new edition, I try to capture these changes while maintaining abroad and comprehensive coverage of the entire field. To begin this process of revision, thetenth edition of this book was extensively reviewed by a number of professors who teachthe subject and by professionals working in the field. The result is that, in many places, thenarrative has been clarified and tightened, and illustrations have been improved.Beyond these refinements to improve pedagogy and u ser- friendliness, there have beensubstantive changes throughout the book. Roughly the same chapter organization has beenretained, but much of the material has been revised and new material has been added. Themost noteworthy changes are as follows:Multichip Modules: A new discussion of MCMs, which are now widely used, has beenadded to Chapter 1. SPEC benchmarks: The treatment of SPEC in Chapter 2 has been updated to cover thenew SPEC CPU2017 benchmark suite. Memory hierarchy: A new chapter on memory hierarchy expands on material that wasin the cache memory chapter, plus adds new material. The new Chapter 4 includes:—Updated and expanded coverage of the principle of locality—Updated and expanded coverage of the memory hierarchy—A new treatment of performance modeling of data access in a memory hierarchy Cache memory: The cache memory chapter has been updated and revised. Chapter 5now includes:— Revised and expanded treatment of logical cache organization, including new figures, to improve clarity—New coverage of content-addressable memory—New coverage of write allocate and no write allocate policies—A new section on cache performance modeling. Embedded DRAM: Chapter 6 on internal memory now includes a section on theincreasingly popular eDRAM. xiiiA01 STAL7193 11 SE FM.indd 131/26/18 9:34 AM

xiv PrefaceAdvanced Format 4k sector hard drives: Chapter 7 on external memory now includesdiscussion of the now widely used 4k sector hard drive format. Boolean algebra: The discussion on Boolean algebra in Chapter 12 has been expandedwith new text, figures, and tables, to enhance understanding. Assembly language: The treatment of assembly language has been expanded to a fullchapter, with more detail and more examples. Pipeline organization: The discussion on pipeline organization has been substantiallyexpanded with new text and figures. The material is in new sections in Chapters 16 (Processor Structure and Function), 17 (RISC), and 18 (Superscalar). Cache coherence: The discussion of the MESI cache coherence protocol in Chapter 20has been expanded with new text and figures. UPPORT OF ACM/IEEE COMPUTER SCIENCE AND COMPUTERSENGINEERING CURRICULAThe book is intended for both an academic and a professional audience. As a textbook, it isintended as a one- or two- semester undergraduate course for computer science, computerengineering, and electrical engineering majors. This edition supports recommendations ofthe ACM/IEEE Computer Science Curricula 2013 (CS2013). CS2013 divides all coursework into three categories: C ore- Tier 1 (all topics should be included in the curriculum); Core- Tier- 2 (all or almost all topics should be included); and Elective (desirable to providebreadth and depth). In the Architecture and Organization (AR) area, CS2013 includes five Tier- 2 topics and three Elective topics, each of which has a number of subtopics. This textcovers all eight topics listed by CS2013. Table P.1 shows the support for the AR Knowledge Area provided in this textbook. This book also supports the ACM/IEEE ComputerEngineering Curricula 2016 (CE2016). CE2016 defines a necessary body of knowledge forundergraduate computer engineering, divided into twelve knowledge areas. One of theseareas is Computer Architecture and Organization (CE-CAO), consisting of ten core knowledge areas. This text covers all of the CE-CAO knowledge areas listed in CE2016. Table P.2shows the coverage.Table P.1 Coverage of CS2013 Architecture and Organization (AR) Knowledge AreaIAS Knowledge UnitsTopicsDigital Logic and DigitalSystems (Tier 2) Machine Level Representation of Data (Tier 2) A01 STAL7193 11 SE FM.indd 14Textbook CoverageOverview and history of computer architectureCombinational vs. sequential logic/Field programmable gate arrays as a fundamental combinationalsequential logic building blockMultiple representations/layers of interpretation(hardware is just another layer)Physical constraints (gate delays, fan- in, fan- out,energy/power)—Chapter 1—Chapter 12Bits, bytes, and wordsNumeric data representation and number bases Fixed- and floating- point systemsSigned and twos- complement representationsRepresentation of non- numeric data (charactercodes, graphical data)—Chapter 10—Chapter 111/26/18 9:34 AM

Preface xvIAS Knowledge UnitsTopicsAssembly Level MachineOrganization (Tier 2) Memory System Organization and Architecture(Tier 2) Interfacing and Communication (Tier 2) Functional Organization(Elective) Multiprocessing andAlternative Architectures(Elective) Performance Enhancements (Elective) A01 STAL7193 11 SE FM.indd 15Textbook CoverageBasic organization of the von Neumann machineControl unit; instruction fetch, decode, and executionInstruction sets and types (data manipulation, control, I/O)Assembly/machine language programmingInstruction formatsAddressing modesSubroutine call and return mechanisms ( cross- reference PL/Language Translation and Execution)I/O and interruptsShared memory multiprocessors/multicoreorganizationIntroduction to SIMD vs. MIMD and the FlynnTaxonomy—Chapter 1—Chapter 8—Chapter 13—Chapter 14—Chapter 15—Chapter 19—Chapter 20—Chapter 21Storage systems and their technologyMemory hierarchy: temporal and spatial localityMain memory organization and operationsLatency, cycle time, bandwidth, and interleavingCache memories (address mapping, block size,replacement and store policy)Multiprocessor cache consistency/Using the memorysystem for inter- core synchronization/atomic memory operationsVirtual memory (page table, TLB)Fault handling and reliability—Chapter 4—Chapter 5—Chapter 6—Chapter 7—Chapter 9—Chapter 20I/O fundamentals: handshaking, buffering, programmed I/O, interrupt- driven I/OInterrupt structures: vectored and prioritized, interrupt acknowledgmentExternal storage, physical organization, and drivesBuses: bus protocols, arbitration, direct- memoryaccess (DMA)RAID architectures—Chapter 3—Chapter 7—Chapter 8Implementation of simple datapaths, includinginstruction pipelining, hazard detection, andresolutionControl unit: hardwired realization vs. microprogrammed realizationInstruction pipeliningIntroduction to instruction- level parallelism (ILP)—Chapter 16—Chapter 17—Chapter 18—Chapter 19Example SIMD and MIMD instruction sets andarchitecturesInterconnection networksShared multiprocessor memory systems and memoryconsistencyMultiprocessor cache coherence—Chapter 20—Chapter 21Superscalar architectureBranch prediction, Speculative execution, Out- of- order executionPrefetchingVector processors and GPUsHardware support for multithreadingScalability—Chapter 17—Chapter 18—Chapter 201/26/18 9:34 AM

xvi PrefaceTable P.2 Coverage of CE2016 Computer Architecture and Organization (AR) Knowledge AreaKnowledge UnitTextbook CoverageHistory and overviewChapter 1—Basic Concepts and Computer EvolutionRelevant tools, standards and/or engineering constraintsChapter 3—A Top-Level View of Computer Function andInterconnectionInstruction set architectureChapter 13—Instruction Sets: Characteristics and FunctionsChapter 14—Instruction Sets: Addressing Modes and FormatsChapter 15—Assembly Language and Related TopicsMeasuring performanceChapter 2—Performance ConceptsComputer arithmeticChapter 10—Number SystemsChapter 11—Computer ArithmeticProcessor organizationChapter 16—Processor Structure and FunctionChapter 17—Reduced Instruction Set Computers (RISCs)Chapter 18—Instruction-Level Parallelism and Superscalar ProcessorsChapter 19—Control Unit Operation and Microprogrammed ControlMemory system organization andarchitecturesChapter 4—The Memory Hierarchy: Locality and PerformanceChapter 5—Cache MemoryChapter 6—Internal Memory TechnologyChapter 7—External MemoryInput/Output interfacing andcommunicationChapter 8—Input/OutputPeripheral subsystemsChapter 3—A Top-Level View of Computer Function andInterconnectionChapter 8—Input/OutputMulti/Many-core architecturesChapter 21—Multicore ComputersDistributed system architecturesChapter 20—Parallel ProcessingOBJECTIVESThis book is about the structure and function of computers. Its purpose is to present, asclearly and completely as possible, the nature and characteristics of modern- day computersystems.This task is challenging for several reasons. First, there is a tremendous variety of products that can rightly claim the name of computer, from s ingle- chip microprocessors costinga few dollars to supercomputers costing tens of millions of dollars. Variety is exhibited notonly in cost but also in size, performance, and application. Second, the rapid pace of changethat has always characterized computer technology continues with no letup. These changescover all aspects of computer technology, from the underlying integrated circuit technologyused to construct computer components to the increasing use of parallel organization concepts in combining those components.In spite of the variety and pace of change in the computer field, certain fundamental concepts apply consistently throughout. The application of these concepts depends onthe current state of the technology and the price/performance objectives of the designer.A01 STAL7193 11 SE FM.indd 161/26/18 9:34 AM

Preface xviiThe intent of this book is to provide a thorough discussion of the fundamentals of computerorganization and architecture and to relate these to contemporary design issues.The subtitle suggests the theme and the approach taken in this book. It has alwaysbeen important to design computer systems to achieve high performance, but never hasthis requirement been stronger or more difficult to satisfy than today. All of the basic performance characteristics of computer systems, including processor speed, memory speed,memory capacity, and interconnection data rates, are increasing rapidly. Moreover, they areincreasing at different rates. This makes it difficult to design a balanced system that maximizes the performance and utilization of all elements. Thus, computer design increasinglybecomes a game of changing the structure or function in one area to compensate for a performance mismatch in another area. We will see this game played out in numerous designdecisions throughout the book.A computer system, like any system, consists of an interrelated set of components.The system is best characterized in terms of structure— the way in which components areinterconnected, and f unction— the operation of the individual components. Furthermore, acomputer’s organization is hierarchical. Each major component can be further described bydecomposing it into its major subcomponents and describing their structure and function.For clarity and ease of understanding, this hierarchical organization is described in this bookfrom the top down:Computer system: Major components are processor, memory, I/O.Processor: Major components are control unit, registers, ALU, and instruction execution unit. Control unit: Provides control signals for the operation and coordination of all processor components. Traditionally, a microprogramming implementation has been used, inwhich major components are control memory, microinstruction sequencing logic, andregisters. More recently, microprogramming has been less prominent but remains animportant implementation technique. The objective is to present the material in a fashion that keeps new material in a clearcontext. This should minimize the chance that the reader will get lost and should providebetter motivation than a b ottom- up approach.Throughout the discussion, aspects of the system are viewed from the points of view ofboth architecture (those attributes of a system visible to a machine language programmer) andorganization (the operational units and their interconnections that realize the architecture).EXAMPLE SYSTEMSThis text is intended to acquaint the reader with the design principles and implementationissues of contemporary operating systems. Accordingly, a purely conceptual or theoreticaltreatment would be inadequate. To illustrate the concepts and to tie them to r eal- world designchoices that must be made, two processor families have been chosen as running examples: Intel x86 architecture: The x86 architecture is the most widely used for nonembeddedcomputer systems. The x86 is essentially a complex instruction set computer (CISC)A01 STAL7193 11 SE FM.indd 171/26/18 9:34 AM

xviii Prefacewith some RISC features. Recent members of the x86 family make use of superscalarand multicore design principles. The evolution of features in the x86 architecture provides a unique case-study of the evolution of most of the design principles in computerarchitecture. ARM: The ARM architecture is arguably the most widely used embedded processor,used in cell phones, iPods, remote sensor equipment, and many other devices. The ARMis essentially a reduced instruction set computer (RISC). Recent members of the ARMfamily make use of superscalar and multicore design principles.Many, but by no means all, of the examples in this book are drawn from these two computerfamilies. Numerous other systems, both contemporary and historical, provide examples ofimportant computer architecture design features.PLAN OF THE TEXTThe book is organized into six parts:IntroductionThe computer system Arithmetic and logic Instruction sets and assembly language The central processing unit Parallel organization, including multicore The book includes a number of pedagogic features, including the use of interactive simulations and numerous figures and tables to clarify the discussion. Each chapter includes a listof key words, review questions, and homework problems. The book also includes an extensiveglossary, a list of frequently used acronyms, and a bibliography.INSTRUCTOR SUPPORT MATERIALSSupport materials for instructors are available at the Instructor Resource Center (IRC) for thistextbook, which can be reached through the publisher’s Web site www.pearson.com/stallings.To gain access to the IRC, please contact your local Pearson sales representative viawww.pearson.com/replocator. The IRC provides the following materials:Projects manual: Project resources including documents and portable software, plussuggested project assignments for all of the project categories listed subsequently in thisPreface. Solutions manual: Solutions to e nd- of- chapter Review Questions and Problems. PowerPoint slides: A set of slides covering all chapters, suitable for use in lecturing. PDF files: Copies of all figures and tables from the book. Test bank: A chapter- by- chapter set of questions. A01 STAL7193 11 SE FM.indd 181/26/18 9:34 AM

Preface xix Sample syllabuses: The text contains more material than can be conveniently coveredin one semester. Accordingly, instructors are provided with several sample syllabusesthat guide the use of the text within limited time. These samples are based on r eal- worldexperience by professors with the first edition.STUDENT RESOURCESFor this new edition, a tremendous amount of original supporting material for studentshas been made available online. The Companion Web Site, at www.pearson.com/stallings,includes a list of relevant links organized by chapter and an errata sheet for the book. To aidthe student in understanding the material, a separate set of homework problems with solutions are available at this site. Students can enhance their understanding of the material byworking out the solutions to these problems and then checking their answers. The site alsoincludes a number of documents and papers referenced throughout the text.PROJECTS AND OTHER STUDENT EXERCISESFor many instructors, an important component of a computer organization and architecture course is a project or set of projects by which the student gets hands- on experience toreinforce concepts from the text. This book provides an unparalleled degree of support forincluding a projects component in the course. The instructor’s support materials availablethrough the IRC not only includes guidance on how to assign and structure the projects butalso includes a set of user’s manuals for various project types plus specific assignments, allwritten especially for this book. Instructors can assign work in the following areas:Interactive simulation assignments: Described subsequently.Research projects: A series of research assignments that instruct the student to researcha particular topic on the Internet and write a report. Simulation projects: The IRC provides support for the use of the two simulation packages: SimpleScalar can be used to explore computer organization and architecturedesign issues. SMPCache provides a powerful educational tool for examining cachedesign issues for symmetric multiprocessors. Assembly language projects: A simplified assembly language, CodeBlue, is used andassignments based on the popular Core Wars concept are provided. Reading/report assignments: A list of papers in the literature, one or more for eachchapter, that can be assigned for the student to read and then write a short report. Writing assignments: A list of writing assignments to facilitate learning the material. Test bank: Includes T/F, multiple choice, and fill- in- the- blank questions and answers. This diverse set of projects and other student exercises enables the instructor to usethe book as one component in a rich and varied learning experience and to tailor a courseplan to meet the specific needs of the instructor and students.A01 STAL7193 11 SE FM.indd 191/26/18 9:34 AM

xx PrefaceINTERACTIVE SIMULATIONSAn important feature in this edition is the incorporation of interactive simulations. Thesesimulations provide a powerful tool for understanding the complex design features of amodern computer system. A total of 20 interactive simulations are used to illustrate keyfunctions and algorithms in computer organization and architecture design. At the relevantpoint in the book, an icon indicates that a relevant interactive simulation is available onlinefor student use. Because the animations enable the user to set initial conditions, they canserve as the basis for student assignments. The instructor’s supplement includes a set ofassignments, one for each of the animations. Each assignment includes several specific problems that can be assigned to students.ACKNOWLEDGMENTSThis new edition has benefited from review by a number of people, who gave generouslyof their time and expertise. The following professors provided a review of the entire book:Nikhil Bhargava (Indian Institute of Management, Delhi), James Gil de Lamadrid (BowieState University, Computer Science Department), Debra Calliss (Computer Science andEngineering, Arizona State University), Mohammed Anwaruddin (Wentworth Instituteof Technology, Dept. of Computer Science), Roger Kieckhafer (Michigan TechnologicalUniversity, Electrical & Computer Engineering), Paul Fortier (University of Massachus

2.4 Basic Measures of Computer Performance 48 2.5 Calculating the Mean 51 2.6 Benchmarks and SPEC 59 2.7 Key Terms, Review Questions, and Problems 66 PART TWO THE COMPUTER SYSTEM 72 Chapter 3 A Top-Level View of Computer Function and Interconnection 72 3.1 Computer Components 73 3.2 Computer Function 75 3.3 Interconnection Structures 90

What is Computer Architecture? “Computer Architecture is the science and art of selecting and interconnecting hardware components to create computers that meet functional, performance and cost goals.” - WWW Computer Architecture Page An analogy to architecture of File Size: 1MBPage Count: 12Explore further(PDF) Lecture Notes on Computer Architecturewww.researchgate.netComputer Architecture - an overview ScienceDirect Topicswww.sciencedirect.comWhat is Computer Architecture? - Definition from Techopediawww.techopedia.com1. An Introduction to Computer Architecture - Designing .www.oreilly.comWhat is Computer Architecture? - University of Washingtoncourses.cs.washington.eduRecommended to you b

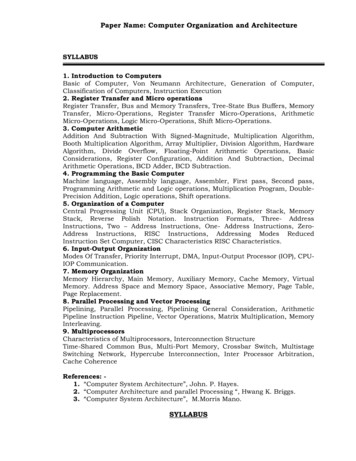

Paper Name: Computer Organization and Architecture SYLLABUS 1. Introduction to Computers Basic of Computer, Von Neumann Architecture, Generation of Computer, . “Computer System Architecture”, John. P. Hayes. 2. “Computer Architecture and parallel Processing “, Hwang K. Briggs. 3. “Computer System Architecture”, M.Morris Mano.

CS31001 COMPUTER ORGANIZATION AND ARCHITECTURE Debdeep Mukhopadhyay, CSE, IIT Kharagpur References/Text Books Theory: Computer Organization and Design, 4th Ed, D. A. Patterson and J. L. Hennessy Computer Architceture and Organization, J. P. Hayes Computer Architecture, Berhooz Parhami Microprocessor Architecture, Jean Loup Baer

COMPUTER ORGANIZATION (3-1-0 ) . Computer System Architecture, Morris Mano, PHI Reference Books: 1. Computer Architecture & Organization, William Stallings, Pearson Prerequisite 1. Knowledge of digital circuit 2. Functionality of various gates . Computer Architecture and Organization, by - John P. Hayes, 3rd Edition, Mc Graw Hill .

1. Computer Architecture and organization – John P Hayes, McGraw Hill Publication 2 Computer Organizations and Design- P. Pal Chaudhari, Prentice-Hall of India Name of reference Books: 1. Computer System Architecture - M. Morris Mano, PHI. 2. Computer Organization and Architecture- William Stallings, Prentice-Hall of India 3.

The first part of Computer Organization and Architecture: Themes and Variations is concerned with the instruction set architecture, and the second part is concerned with computer organization which described an ISA is actually implemented. Today, the term microarchitecture has largely replaced the computer organization. In this workbook, we are .

Computer Architecture: David A. Patterson and John L. Hennessy, Computer Organization and Design: The Hardware/Software Interface, Elsevier. Carl Hamachar, Zvonco Vranesic and Safwat Zaky, Computer Organization, McGraw-Hill. John P. Hayes, Computer Architecture and Organization, McGraw-Hill. Operating System:

John P Hayes “Computer Architecture and organization” McGraw Hill 2. Dezso Sima,Terence Fountain and Peter Kacsuk “ Advanced Computer Architecture” Pearson Education 3. Kai Hwang “ Advanced Computer Architecture” TMH Reference Books: 1. Linda Null, Julia Lobur- The Essentials of Computer Organization and Architecture, 2014, 4th .