Design Of Voltage Boosting Rectifiers For Wireless Power Transfer Systems

DESIGN OF VOLTAGE BOOSTING RECTIFIERS FOR WIRELESS POWER TRANSFER SYSTEMS Ramaa Saket Suri Thesis Prepared for the Degree of MASTER OF SCIENCE UNIVERSITY OF NORTH TEXAS May 2019 APPROVED: Ifana Mahbub, Major Professor Kamesh Namuduri, Committee Member Parthasarathy Guturu, Committee Member Shengli Fu, Chair of the Department of Electrical Engineering Hanchen Huang, Dean of the College of Engineering Victor Prybutok, Dean of the Toulouse Graduate School

Suri, Ramaa Saket. Design of Voltage Boosting Rectifiers for Wireless Power Transfer Systems. Master of Science (Electrical Engineering), May 2019, 29 pp., 2 tables, 28 figures, 21 numbered references. This thesis presents a multi-stage rectifier for wireless power transfer in biomedical implant systems. The rectifier is built using Schottky diodes. The design has been simulated in 0.5µm and 130nm CMOS processes. The challenges for a rectifier in a wireless power transfer systems are observed to be the efficiency, output voltage yield, operating frequency range and the minimum input voltage the rectifier can convert. The rectifier outperformed the contemporary works in the mentioned criteria.

Copyright 2019 by Ramaa Saket Suri ii

ACKNOWLEDGEMENTS I would like to extend my sincere gratitude to my advisor Dr. Ifana Mahbub. She has supported me throughout my research journey giving me valuable inputs and suggestions. My thanks to the Dr. Parthasarathy Guturu and Dr. Kamesh Namuduri for their constructive comments on my research. I would also like to thank the Department of Electrical Engineering for providing the equipment needed for the research. My co-researchers in the iBioCAS lab have been very supportive and helpful and I sure made some good friends. I would like to thank my parents who have been encouraging me and kept my motive high to successfully finish my Master’s degree. Last but not the least, my love to all my dear friends who kept my spirits high throughout my time at UNT. iii

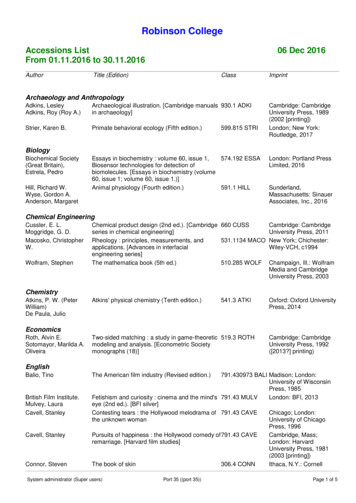

TABLE OF CONTENTS Page ACKNOWLEDGEMENTS . iii LIST OF TABLES . v LIST OF FIGURES . vi CHAPTER 1. INTRODUCTION . 1 1.1 1.2 Motivation . 1 1.1.1 Near-Field Region . 2 1.1.2 Far-Field Region . 2 Thesis Organization . 3 CHAPTER 2. LITERATURE REVIEW . 5 2.1 Half-Wave Rectifier . 5 2.2 Full-Wave Rectifier . 6 2.3 Rectifier Architectures . 8 CHAPTER 3. DESIGN ARCHITECTURE . 15 3.1 Schottky Diode. 15 3.2 Proposed Architecture . 17 3.2.1 One-Stage Architecture . 18 3.2.2 10-Stage Architecture . 18 3.2.3 10-Stage Characterization . 19 CHAPTER 4. SIMULATION RESULTS . 21 4.1 0.5µm Process . 21 4.2 130nm Process . 23 CHAPTER 5. CONCLUSION AND FUTURE WORKS . 26 REFERENCES . 28 iv

LIST OF TABLES Page Table 4.1: Performance comparison of 0.5µm rectifier and related works . 23 Table 4.2: Performance comparison of 130nm rectifier and related works . 25 v

LIST OF FIGURES Page Fig. 1.1: Optogenetic Implant . 1 Fig. 1.2: A typical wireless power transfer system . 2 Fig. 2.1: Half-wave rectifier. 5 Fig. 2.2: Full-wave rectifier . 7 Fig. 2.3: Rectifier topologies: (a) NMOS differential-drive bridge rectifier, (b) NMOS differential-drive gate cross-connected bridge rectifier, (c) NMOS doubler, (d) NMOS-PMOS differential-drive gate cross-coupled bridge rectifier [6]. . 8 Fig. 2.4: Control circuit proposed in [7] . 9 Fig. 2.5: N-Stage voltage doubler proposed in [8]. 10 Fig. 2.6: One-stage bridgeless boost converter proposed in [10] . 11 Fig. 2.7: Improved bridgeless boost converter proposed in [11] . 11 Fig. 2.8: Three-stage rectifier proposed in [13] . 12 Fig. 2.9: Rectifier with bootstrap capacitor proposed in [17] . 12 Fig. 2.10: Block diagram of the three-stage voltage multiplier used in [18] . 13 Fig. 2.11: First stage of the voltage multiplier used in [18] . 13 Fig. 3.1: Energy band-diagram of a p-n junction [20] . 15 Fig. 3.2: Energy band-diagram of a metal-semiconductor Schottky contact [20] . 16 Fig. 3.3: I-V Characteristics of a Schottky diode. 16 Fig. 3.4: I-V Characteristics of a MOSFET . 16 Fig. 3.5: Rectifier Architecture . 17 Fig. 3.6: One-Stage Architecture working principle . 18 Fig. 3.7: 10-Stage architecture working principle . 19 Fig. 3.8: Power consumption with output DC voltages for different stages [9] . 20 Fig. 4.1: 0.5μm Schottky Diode I-V Characteristics [9] . 21 vi

Fig. 4.2: Output DC voltages for each stage [9] . 21 Fig. 4.3:Vdc vs Frequency [9] . 22 Fig. 4.4:Vin vs VCE [9] . 22 Fig. 4.5: I-V Characteristics of 130nm Schottky Diode . 24 Fig. 4.6: Output voltage for various input voltages. . 24 Fig. 4.7: Output voltage of the rectifier for a wide frequency range of input signal. . 25 vii

CHAPTER 1 INTRODUCTION 1.1 Motivation Biomedical implants are millimeter-scale devices which are implanted inside a living organism to replace or to enhance a part of the body. In biomedical implants like optogenetic implants (Fig. 1.1) where the device is implanted close to the brain of the mouse, installing a battery to run the implant is not recommended as there is a risk of the battery leaking and affecting the brain. Instead, implementing a near-field wireless power transmission system to power the implant will avoid any potential risks. The need to remove battery sources in biomedical implants motivates the study of wireless power transfer [4]. The major criteria for designing a wireless power transfer (WPT) are size, efficiency and the power-transfer distance [4]. The size of the device is required to be small in order to be implanted. A typical wireless power transfer system achieves an efficiency of 45% to 80%, so there is a need to keep a check on the efficiency. as the power transfer distance is in the range of millimeters [4]. Fig. 1.1: Optogenetic Implant Wireless power transfer technology for various biomedical implant systems and portable electronic devices has improved in terms of operation frequency range, transferring low power across short distances [1]. With the increase in requirement of the power conversion efficiency, WPT systems working with signals which have frequencies in the range of MHz have been 1

implemented in the recent times [2,3]. Wireless power transfer systems can be classified into farfield WPTs and near-field WPTs. Far-field and near-field are radiation regions of the electromagnetic field around a transmitting device such as an antenna. 1.1.1 Near-Field Region As defined by Constantin A. Balanis (2005), Near-field is a region around a radiating device where the radiation is predominant and the distribution of the angular component of the EM field depends upon the distance from the antenna [5]. The near-field exists around the antenna for a radial distance R 2D2/λ, where D is the largest antenna dimension and λ is the wavelength of the radiating signal. Examples for near-field WPTs are inductive coupling, magnetic coupling and capacitive coupling [4]. 1.1.2 Far-Field Region Far-field radiation region exists for a radial distance R 2D2/λ in the radiating field around the antenna, where D is the largest antenna dimension and λ is the wavelength of the radiating signal. Examples for far-field WPT systems are LASER, RF, Microwave etc. Fig. 1.2: A typical wireless power transfer system 2

For the short-range wireless power transfer in implant devices, inductive coupling is most commonly used [4]. The block diagram of a traditional WPT module implementing inductive coupling is illustrated in Fig. 1.2. It has an AC power source which generates an AC electromagnetic signal that is transmitted to the receiver coil. The transmitter coil (L1) radiates the signal which is picked up by the receiver coil (L2). Fig. 1.2 denotes the inductive coupling technique. The AC signal on the receiver coil L2 is fed to a rectifier which converts the AC signal to a DC signal and passes it on to the implant device. Recent CMOS-based WPT systems discussed in [4] show efficiencies ranging from 45% to 80%. Rectifiers are one of the most important blocks in a wireless power transfer system, as the whole AC power received is rectified and supplied to the load by the rectifier. For this reason, it is required that the rectifier has a very high efficiency. The rectifier discussed in this thesis is designed to operate in a near-field wireless power transfer system which has an operating frequency from 10 KHz to 100 MHz and input voltages in the range of 200 mV. 1.2 Thesis Organization This thesis is organized as follows. The concept of WPT systems in biomedical implant systems and the function of rectifiers in a WPT are discussed. Chapter 2 introduces the concept of rectifiers and the two basic rectifier structures. It is followed by a literature review for various rectifier architectures designed for wireless power transfer systems. Chapter 3 discusses the design architecture of the Schottky diode rectifier, also outlining the properties and importance of the Schottky diode. 3

Chapter 4 showcases the simulation results of the proposed architecture designed in 0.5µm CMOS and 130nm CMOS processes. The conclusions are presented in Chapter 5. The results are recalled, and the future works are discussed. 4

CHAPTER 2 LITERATURE REVIEW Rectifier is a circuit which is designed to convert an AC signal into a DC signal. They are used when the system has an AC source and needs to supply power to a DC load. Starting with traditional diode-bridge rectifiers, many architectures have been proposed to this day. Rectifiers are divided into two types: Half-wave rectifiers and full-wave rectifiers. 2.1 Half-Wave Rectifier A half-wave rectifier passes only one-half of the sine wave to convert it to a DC signal. A half-wave rectifier built using diodes is shown in the Fig 2.1. A single diode is used in a half-wave rectifier. An AC signal is fed through the input terminals into the rectifier. The output is observed on a load R. During the positive half-cycle of the sine-wave, the diode is forward biased as the anode of the diode is at a higher potential with respect to the cathode, and the current flows through the diode. The positive half-cycle of the signal is observed at the load. During the negative halfcycle of the sine-wave, the diode is reverse biased, as the anode is at a lower potential with respect to the cathode, and no voltage is transferred to the load. The output waveform is shown in the Fig. 2.1. As only 50% of the input sine-wave is rectified, the rectifier is called a half-wave rectifier. I Diode AC input R Fig. 2.1: Half-wave rectifier 5 Vout

If VMAX and IMAX are the maximum voltage amplitude and the maximum current amplitude of the sinusoidal wave, then the average output voltage and output current are given by, VAV VMAX/ π 0.318*VMAX (1) IAV IMAX/ π 0.318*IMAX (2) The efficiency is given by the ratio of output power to input power. The output DC power (PDC) is given by, PDC VMAX*IMAX/(π)2 (3) The input power (PAC) is given by, PAC (VMAX/2)*(IMAX/2) (4) η (2/π)2 0.406 (5) The efficiency is given by, The efficiency of a half-wave rectifier is equal to 40.6%. That is, of all the AC power that is sent through the input, only 40.6% of it is rectified, i.e. converted into DC power. 2.2 Full-Wave Rectifier A full-wave rectifier passes both the positive and negative half-cycles of the input sinusoidal wave. A full-wave diode rectifier is shown in Fig. 2.2. Four diodes are used in a fullwave rectifier and a capacitor is used as a load. During the positive half cycle, the diodes D3 and D4 are reverse biased, D1 and D2 are forward biased. The current flows through D1 and D2, charging the capacitor to the peak voltage of the sinusoid. In the negative half cycle, the diodes D3 and D4 are forward biased, D1 and D2 are reverse biased. The current flows through D3 and D4, charging the capacitor again to the peak of the input sinusoidal signal. The output waveform 6

of a full-wave rectifier is shown in Fig. 2.2. A full-wave rectifies converts 100% of the input AC signal to DC. Vac Vrect Fig. 2.2: Full-wave rectifier If VMAX and IMAX are the maximum voltage amplitude and the maximum current amplitude of the sinusoidal wave, then the average output voltage and output current are given by, VAV 2*VMAX / π 0.636*VMAX (6) IAV 2*IMAX / π 0.636*IMAX (7) The efficiency of a full-wave rectifier is defined as the ratio of the output DC power to the input AC power. The output power is given by, PDC 2*VMAX*IMAX/(π)2 (3) PAC 2*(VMAX/2)*(IMAX/2) (4) The input power is given by, The efficiency (PDC/PAC) is given by, η 2*(2/π)2 0.812 (5) The efficiency of a full wave rectifier is 81.2%, which is twice the efficiency of a half-wave rectifier. 7

2.3 Rectifier Architectures Rectifier architectures working at low-input voltages are explored in this literature. Mazzilli, Francesco, et al. discusses four standard architectures of rectifier circuits [6]. Fig. 2.3 (a) is a standard NMOS bridge rectifier. For rectification, this architecture requires the input voltage to be twice the threshold voltage of the transistors, to turn on the rectifier. This limits the input voltage to be higher than twice the threshold, and to rectify voltages lower than that, devices with lower threshold voltage are to be implemented. Fig. 2.3 (b) is a gate cross-connected bridge rectifier, where the gates of the NMOS transistors are cross-connected. Cross-connecting the gates increases the gate-source voltage of the transistors, thereby reducing the voltage required to turn the transistor on, i.e. the threshold voltage. Fig. 2.3: Rectifier topologies: (a) NMOS differential-drive bridge rectifier, (b) NMOS differentialdrive gate cross-connected bridge rectifier, (c) NMOS doubler, (d) NMOS-PMOS differential-drive gate cross-coupled bridge rectifier [6]. Fig. 2.3 (c) is a standard voltage doubler circuit which rectifies the input AC voltage and doubles the voltage level. The transistors act as switches charging the capacitor C to the input voltage during the positive half cycle of the input. During the negative half cycle, the capacitor C 8

gets charged to twice the input voltage and discharges through M10 thereby charging the output capacitor to twice the input voltage. The drop across the transistors is required to be as low as possible to achieve higher efficiencies. Multiple stages of the voltage doubler can be cascaded to achieve a higher voltage conversion efficiency (VCE), which is the ratio of the output DC voltage to the input AC RMS voltage. Fig. 2.3 (d) is a gate cross-coupled bridge rectifier with NMOS and PMOS transistors. The usage of both NMOS and PMOS improves the efficiency as the NMOS-PMOS pairs act as switches in both the positive and negative half-cycles of the input, instead of just one half-cycle. This helps in yielding a DC voltage higher than the other four architectures. The drawback of using an NMOS-PMOS rectifier is, a reverse current flows from the output to input when the input voltage while oscillating, falls below the output DC voltage. This causes the efficiency of the rectifier to drop. To avoid this effect, the NMOS-PMOS rectifier circuits are accompanied by a control circuit. A simple control circuit has been proposed in [7]. Two NMOS-PMOS inverters are connected to the PMOS switches to turn the diodes off when they start conducting in the reverse direction (Fig. 2.4). Fig. 2.4: Control circuit proposed in [7] 9

Fig. 2.5: N-Stage voltage doubler proposed in [8] [8] presents a multi-stage NMOS-based voltage doubler circuit. The circuit is shown in Fig. 2.5. A detailed analysis of the characterization of an NMOS-based voltage doubler is discussed in the section II of the [8]. The design has been optimized for two cases: maximum voltage and maximum efficiency. The optimum transistor sizing and the optimal number of stages yield an efficiency of 17.6% for the maximum voltage approach and an efficiency of 30.5% for the maximum efficiency approach. While designing a multi-stage rectifier for a low-power system, it is important to consider the sizing of the devices, the number of stages and the efficiency. A review on voltage boosting circuitry for low-power transfer applications is presented in [9]. It outlines various contemporary boost rectifier architectures designed for low-power applications [10]-[14]. Various NMOS-based bridge rectifiers [12], [13] and diode-based architectures [10], [11], [14] have been discussed. A novel bridgeless boost rectifier is proposed in [10]. The circuit is designed using diodes arranged as shown in Fig. 2.6. The bridgeless structure has a high output current ripple. To solve this issue, a bridgeless interleaving boost converter is proposed in [11] (Fig. 2.7). Compared to the 10

boost converter in [10], the total loss observed in the bridgeless interleaving boost converter is lower than the standard bridgeless boost converter. Fig. 2.6: One-stage bridgeless boost converter proposed in [10] An inductive power management system has been proposed in [12]. It has a rectifier constructed using NMOS transistors connected to form a rectifier. The maximum efficiency reported for 10mW is 77%. A three-stage full-wave rectifier is designed for an energy harvesting system in [13]. The architecture is shown in Fig. 2.8. The capacitor banks CC are used to tune the rectifier to the antenna. The NMOS rectifier achieves an efficiency of 31.5% for -15dBm input power. Fig. 2.7: Improved bridgeless boost converter proposed in [11] The architectures discussed above achieve efficiencies less than 80% for an input power less than 10mW. There is a need to obtain higher efficiencies for lower input voltages, as the target 11

applications like the optogenetic implants operate with voltages below 200mV. Fig. 2.8: Three-stage rectifier proposed in [13] Another important design parameter of a rectifier is its frequency range of operation. According to [15] and [16], the optimum frequency for inductively-coupled WPT systems is in the 100MHz frequency range, in the presence of a biological tissue. Khan, Mohd Tauheed et.al. presents a rectifier (Fig. 2.9) designed in the 32nm CMOS process which uses a bootstrap capacitor in the circuit to reduce the forward voltage drop [17]. Fig. 2.9: Rectifier with bootstrap capacitor proposed in [17] 12

As NMOS transistors have low input impedance, a capacitor is connected at the input to increase the input impedance, thereby turning the NMOS transistor for a lower voltage. The rectifier is found to be stable up to the 40 MHz – 50 MHz frequency range. The efficiency of the rectifier is observed to drop rapidly for frequencies above 50 MHz. Fig. 2.10: Block diagram of the three-stage voltage multiplier used in [18] Fig. 2.11: First stage of the voltage multiplier used in [18] Asmeida, Akrem, et al. talks about a three-stage voltage multiplier for an RF energy harvesting circuit [18]. The rectifier model uses Schottky diodes for rectification. The block diagram of the three-stage voltage multiplier is shown in the Fig. 2.10. The received signal from the UWB antenna is fed to the rectifier through a matching circuit. Each stage of the three-stage 13

rectifier is a voltage multiplier shown in Fig. 2.11. The rectifier is observed to be operating in 1.8 GHz to 2.4 GHz. The rectifier achieves a maximum efficiency of 86% for an input voltage of 3.75V. Schottky diodes have very low threshold voltages, and hence are used for faster switching [19]. The prime challenges in designing a rectifier for a biomedical implant system are The efficiency. The output voltage yield. The minimum input voltage the rectifier can convert. The operating frequency ranges. 14

CHAPTER 3 DESIGN ARCHITECTURE Considering the design challenges mentioned in the previous chapter, a multi-stage rectifier design with Schottky diodes is presented. 3.1 Schottky Diode Unlike a standard diode with a semiconductor-semiconductor junction, Schottky diodes have a metal-semiconductor junction which allows them to turn-on at a much lower voltage, which is usually in the range of 100 mV – 700 mV. Looking at the energy band diagrams of p-n junction and the metal-semiconductor Schottky junction from figures 3.1 and 3.2 [20], the depletion region in the Schottky contact is much lower than the p-n junction contact. Due to the lower potential barrier, Schottky diodes have a lower threshold voltage and hence reduces the power consumption. Fig. 3.1: Energy band-diagram of a p-n junction [20] 15

Fig. 3.2: Energy band-diagram of a metal-semiconductor Schottky contact [20] The I-V characteristics of a Schottky diode with non-ideal behavior are given by [21], I IS [exp(qVD)/nKT)-1] (5) where IS is the reverse saturation current, q is the electronic charge, VD is the voltage across the diode, n is a dimensionless parameter called the ideality factor, k is the Boltzmann constant, and T is the absolute temperature. Fig. 3.3: I-V Characteristics of a Schottky diode Fig. 3.4: I-V Characteristics of a MOSFET The I-V characteristics curve of a 0.5µm CMOS process Schottky diode is shown in the Figure 3.3. The diode starts conducting for a voltage above the forward voltage which is close to 16

100 mV. The I-V characteristics of a 0.5µm CMOS process MOS transistor can be seen in Figure 3.4. From the figures, the forward/threshold voltage of a Schottky diode is lower than a MOSFET by 500 mV. The forward voltage (Vf) of the Schottky diode varies with the technology process. The Vf of the Schottky diode in the 0.5µm CMOS process is 0.142V (Fig. 3.3). The threshold voltage of the Schottky diode also depends upon the sizing. The size is characterized by the length and width. A longer channel (longer width) increases the threshold voltage, as the depletion barrier increases. So, the width of the diode has to be adjusted so that the diode turns on for a minimum threshold voltage. 3.2 Proposed Architecture The proposed rectifier is a 10-stage voltage-doubler. Figure 3.5 shows the architecture of the rectifier. The rectifier is built using 20 Schottky diodes and 20 capacitors. The characterization of 10-stages is discussed in section 3.2.3. Fig. 3.5: Rectifier Architecture 17

3.2.1 One-Stage Architecture To understand the working principle of the rectifier, it is important to understand the working of the first single-stage of the rectifier (Fig 3.6). Fig. 3.6: One-Stage Architecture working principle Consider an AC signal Vmcosωt where Vm is the amplitude, is given as an input to the rectifier. During the negative half cycle, the diode D1 is turned on, D2 is turned off and the capacitor C1 is charged to an amplitude of Vm. During the next positive cycle, the diode D1 is turned off, D2 is turned on, and the capacitor C1 gets charged to a voltage 2Vm and discharges through D1 thereby charging C2 to a voltage 2Vm. This is in an ideal scenario without considering the voltage drop across the Schottky diode. Considering the forward voltage of the diode, the output voltage of one stage is given as, Vout 2*(Vm – Vdiode) (6) where Vdiode is the forward voltage of the Schottky diodes. 3.2.2 10-Stage Architecture The single stage discussed above is cascaded with 9 more single-stages to form a multistage system. The voltage is doubled at the end of each stage, and the at the end of 10-stages, the equivalent voltage will be 2*10 times the input voltage. Fig. 3.7 shows the 10-stage architecture. For an input voltage of say Vm, the voltage output at 10-stages will be 2*10*(Vm – Vdiode). 18

Fig. 3.7: 10-Stage architecture working principle To generalize the output voltage for N-stages, the output DC voltage can be defined as, VDC 2*N*( Va – Vdiode) (7) 3.2.3 10-Stage Characterization Maximum output voltage is a prime characteristic for a voltage boosting rectifier. Ideally, the output voltage increments as the number of stages are increased. But, as the number of stages are increased, the total power consumed also increases, as the components in each stage consume a certain amount of power. The power consumed through each stage is the power consumed by the diodes and the capacitors. Fig. 3.8 shows the output voltage and power consumption of the circuit for 10 and 12 stages. From the figure, the output voltages for the 10 and 12 stages are comparable, but the power consumption in the 12-stage design is greater than the 10-stage design. It shows that, as the number of stages is increased, the output voltage surely increases, but the energy lost through the stages also increases. A trade-off between the power consumption and the number of stages has been made to produce the required output with minimum losses. 19

Fig. 3.8: Power consumption with output DC voltages for different stages [9] 20

CHAPTER 4 SIMULATION RESULTS The circuit has been designed and simulated using the Cadence Virtuoso Custom IC Design Tool in the 0.5µm CMOS process and the 130nm CMOS process libraries. The performance of the circuit varies from process to process as the properties of the components change with the process. As the 130nm CMOS process has smaller process parameters than the 0.5µm CMOS process, performance variation of the circuit in both the processes is expected. The circuit performance has been tested in terms of output voltage boost, operating frequency range, voltage conversion efficiency and power conversion efficiency. 4.1 0.5µm Process The results of the proposed rectifier in the 0.5µm CMOS process are published in [9]. The I-V characteristics of the Schottky diode in this process are shown in the Figure 4.1. The forward voltage of the Schottky diode is about 160 mV in this process. Fig. 4.1: 0.5μm Schottky Diode I-V Characteristics [9] 21 Fig. 4.2: Output DC voltages for each stage [9]

Fig. 4.3:Vdc vs Frequency [9] Fig. 4.4:Vin vs VCE [9] The len

Rectifiers are divided into two types: Half-wave rectifiers and full-wave rectifiers. 2.1 Half-Wave Rectifier A half-wave rectifier passes only one-half of the sine wave to convert it to a DC signal. A half-wave rectifier built using diodes is shown in the Fig 2.1. A single diode is used in a half -wave rectifier.

DC DRIVES USING CONTROLLED RECTIFIERS 13.1 INTRODUCTION The speed of d.c. motor can be controlled very easily by means of regulating its supply voltage by the use of phase controlled rectifiers. This control can be applied to either the field or the armature circuit. The motor response

SYMBOLS AND DEFINITIONS Symbol Definition V WM Working Standoff Voltage: The voltage across the TVS in its off, non-conducting state. V BR Breakdown Voltage: The minimum voltage at which avalanche breakdown begins and the TVS starts conducting. P PP Peak Pulse Power: The peak power that can be applied for a specific pulse width and waveform. I

SYMBOLS AND DEFINITIONS Symbol Definition V WM Working Standoff Voltage: The voltage across the TVS in its off, non-conducting state. V BR Breakdown Voltage: The minimum voltage at which avalanche breakdown begins and the TVS starts conducting. P PP Peak Pulse Power: The peak power that can be applied for a specific pulse width and waveform. I

this double-tier design the transformer is connected to two six-pulse rectifiers, adding up to a 12-pulse system or two parallel 6-pulse systems. The regulation of the LV transformer voltage is normally done by using a NLTC in the primary winding. The location of the 6-pulse rectifiers can be on the same si

Elettra Synchrotron Light Laboratory, Trieste, Italy Abstract In particle accelerators, rectifiers are u sed to convert the AC voltage into DC or low-frequency AC to supply loads like magnets or klystrons. Some loads require high currents, others high

Pulse width-modulation (PWM) rectifiers in distribution systems represents the best solution, in terms of performance and effectiveness, for elimination of harmonic distortion as well as power factor correction, balancing of loads, voltage regulation and flicker com

Power Electronics Single Phase Controlled Rectifiers 1 Dr. Firas Obeidat . 2 . The power absorbed by the resistor is . The first figure shows a fully controlled bridge rectifier, which uses four thyristors to control the average load voltage.

Archaeological illustration. [Cambridge manuals in archaeology] 930.1 ADKI Cambridge: Cambridge University Press, 1989 (2002 [printing]) Strier, Karen B. Primate behavioral ecology (Fifth edition.) 599.815 STRI London; New York: Routledge, 2017 Biology Biochemical Society (Great Britain), Estrela, Pedro Essays in biochemistry : volume 60, issue 1, Biosensor technologies for detection of .