Joint Design-Time And Post-Silicon Minimization .

Joint Design-Time and Post-Silicon Minimization of ParametricYield Loss using Adjustable Robust OptimizationMurari Mani, Ashish K. Singh, and Michael OrshanskyDepartment of Electrical and Computer Engineering, University of Texas at Austinmani@ece.utexas.eduavailability of post-silicon adaptivity in synthesizing the circuit.Two powerful and complementary strategies for reducing leakageconsidering variability are pre-silicon statistical designoptimization and post-silicon adaptivity. There is a growing bodyof work on statistical circuit analysis methods [1-3] (i.e., SSTA)and statistical post-synthesis optimization [4-6], including sizingand dual-threshold voltage assignment algorithms. These toolsshow promise in reducing parametric yield loss, or alternatively,reducing power consumption while maintaining high yield: insome cases, a 25% reduction in power is gained at the cost of 5%timing yield loss. The growing magnitude and complexity ofuncertainty is bound to make post-synthesis optimizationtechniques insufficient in guaranteeing reliable circuit operationwith reasonable parametric yield.Post-silicon design adaptivity, or tuning, currently includesseveral techniques; the primary ones being adaptive body biasing(ABB) and adaptive supply voltage (ASV). ABB uses the bodyeffect to modulate the threshold voltages of transistors, therebycontrolling leakage and performance [7-10]. ASV raises thepower supply (Vdd) for slow (low-leakage) dies, and lowers it forfast (high-leakage) dies, ensuring better overall yield [11]. It relieson the roughly cubic dependence of leakage power on Vdd inCMOS circuits (also impacting dynamic power quadratically). Inthe future, a larger palette of tuning tools is likely to emerge:recently, an adaptive-size tapered Pareto buffer was designed withcontrol facilitated via a tri-state buffer [12].A widespread industrial adoption of adaptive techniques is not yetpossible for two reasons. One is that designers do not have thetools to help them decide whether, and how much, adaptivecircuitry is needed, or what type of post-silicon tuning techniquewill be most appropriate. The availability of both design-time(pre-silicon) optimization and post-silicon adaptivity leads to arich optimization space in which coordination between the twolevels is required. Sizing can be used to upsize the gates beyondthe need of a nominal design to achieve higher timing yield, butwith increased power. Alternatively, the adaptivity of thresholdvoltage can be used to tighten the speed distribution to improveyield. Depending on the magnitude and the spatial structure ofvariability, the two approaches will have different costeffectiveness, i.e., they will be characterized by different Paretocurves in the space of design objectives.Algorithmically, future robust circuit synthesis can beconceptualized as a two-stage optimization problem, withadditional second-stage tuning available upon the realization ofuncertain variables. In this paper an efficient formulation isproposed using the theory of adjustable optimization. Thisoptimization paradigm presumes that the decision-maker has achance to update his optimization strategy upon learningadditional information. If the objective function is linear in thedecision variables, then, under the conditions that the uncertaintyABSTRACTParametric yield loss due to variability can be effectively reducedby both design-time optimization strategies and by adjustingcircuit parameters to the realizations of variable parameters. Thetwo levels of tuning operate within a single variability budget,and because their effectiveness depends on the magnitude and thespatial structure of variability their joint co-optimization isrequired. In this paper we develop a formal optimizationalgorithm for such co-optimization and link it to the control andmeasurement overhead via the formal notions of measurementand control complexity.We describe an optimization strategy that unifies design-timegate-level sizing and post-silicon adaptation using adaptive bodybias at the chip level. The statistical formulation utilizesadjustable robust linear programming to derive the optimal policyfor assigning body bias once the uncertain variables, such as gatelength and threshold voltage, are known. Computationaltractability is achieved by restricting optimal body bias selectionpolicy to be an affine function of uncertain variables. Wedemonstrate good run-time and show that 5-35% savings inleakage power across the benchmark circuits are possible.Dependence of results on measurement and control complexity isstudied and points of diminishing returns for both metrics areidentified.Categories and Subject DescriptorsB.7.2 [Integrated Circuits]: Logic Design- optimizationGeneral TermsAlgorithms, Design, Reliability1. INTRODUCTIONIncreased variability of device parameters necessitates thedevelopment of a new generation of circuit synthesis CAD tools.In addition, the increases in variability and power consumptionare closely related because of the exponential dependence ofleakage on some process and environment parameters. Twofundamental paradigms are available for dealing with variability:statistical design (optimization at design time) and post-siliconadaptivity (on-line tuning). To guarantee reliable circuit operationwith minimal power consumption, next-generation circuitsynthesis techniques for robustness must explicitly account for thePermission to make digital or hard copies of all or part of this work forpersonal or classroom use is granted without fee provided that copiesare not made or distributed for profit or commercial advantage and thatcopies bear this notice and the full citation on the first page. To copyotherwise, or republish, to post on servers or to redistribute to lists,requires prior specific permission and/or a fee.ICCAD'06, November 5-9, 2006, San Jose, CACopyright 2006 ACM 1-59593-389-1/06/0011. 5.0019

sets are affine functions of some parameters, the optimal policyfor the second-stage decisions can be computed efficiently. Twostage stochastic optimization problems are difficult to solve [13].However, recent developments in the theory of convexprogramming have enabled the solution of robust versions oflinear and quadratic programs, which can be expressed as secondorder conic programs or semi-definite programs [14, 15].Extending these solution methods to adjustable robustprogramming has been demonstrated in [16]. In this paper, webuild upon this work to develop an efficient solution to the postsilicon optimization problem under variability.The problem is formulated in the following way. The first-stage(design-time) power-delay optimization is done via sizing, andsecond-stage (post-silicon) optimization is achieved by body biastuning. The second stage decision variables are represented asaffine function of parameter uncertainty. The solution to thisoptimization problem is a design time decision (size of gates inthe circuit) and an optimal policy that prescribes the amount ofbias depending on the realizations of uncertain variables (e.g. gatelength, Vth on a specific chip). Initial experiments prove that theoptimal synergy between design-time and post-siliconoptimization depends on the amount and structure of variability.If variability is highly spatially correlated within the chip, designtime optimization will be ineffective and may even lead to largeyield losses. On the other hand, with the increase of intra-chipvariability, the effectiveness of post-silicon adaptivity decreases.Three measures of complexity that parameterize the solution andthe optimality of this problem are introduced by us: the controlcomplexity (the granularity of control), the measurementcomplexity (the granularity of the monitoring and sensingcircuitry), and the parameter complexity (a measure of howspatially uncorrelated the process variable is). Using thesemetrics, formal quantitative trade-offs between design-time andpost-silicon adaptivity can be identified. Such capability will alsobe useful for the analysis and development of the fine-granularcontrol structures, e.g. for determining the spatial granularity.The rest of the paper is organized as follows. Section 2 motivatesthe need for joint co-optimization between design-time and postsilicon optimization. Section 3 presents the leakage and delaymodels used. The details of the algorithm are presented in Section4 followed by the results and analyses in Section 5.both by slower chips and chips that are too fast, because they aretoo leaky.The fundamental limitation of design-time methods is that theyimpose an overhead on each instance of the fabricated chip sincethey intrinsically lack the ability to "react" to the actualconditions on the chip. For example, when using sizing for timingoptimization they impose a fixed area overhead that may bewasteful on some instances of the ICs that would meet timingeven with smaller driver sizes. Having an adjustable-width driverwould be ideal, since it could ensure meeting constraints with theminimum overhead for each chip.The problem that we address in this paper is how to performdesign-time circuit optimization and post-silicon tuning jointly.Why should these two steps be coordinated, i.e., why do we needjoint co-optimization? The two methods operate from differentviewpoints: in design-time optimization a decision (e.g., sizing)must be made before the realization of uncertainty (gate length),while in post-silicon tuning of the decision (the value of bias toapply) is made after the realization of uncertainty, i.e., when thechip's physical properties have been determined duringmanufacturing.However, the two paradigms operate within a single budget ofuncertainty, and thus meeting constraints can be achieved by bothmethods. But their cost-effectiveness depends on specificconditions, such as the spatial correlation of process variability,the granularity of adaptivity that can be implemented, and themagnitude of leakage power in comparison with the switchingpower. The objective of this paper is to develop formal means andoptimization methods that will allow joint optimization. Thespecific optimization strategy will jointly consider the amount ofvariability and cost-effectiveness of power reduction strategies, toderive a policy that will guide post-silicon tuning, as well as makethe first-phase design decisions. This will allow to optimallypartition the design space between these levels of hierarchy.Formally, the objective of the algorithm we develop is tominimize the expected value of leakage power under a givendelay constraint T at a given yield amin El,ak s.t. P(D T) aThis formulation is generic and, different specific optimizationmechanisms can be studied. In this paper we focus on sizing andadaptive body bias for threshold control at the chip level, withonly a small number of partitions of the chip into individuallytunable clusters. The widely different spatial scales involved inthis problem are of some interest and are actively explored. In theabove formulation, the objective function and the constraintsdepend on both the design time optimization variables (sizes) andthe post silicon decision variables (body biases). The problem canbe formally viewed as a two-phase optimization under uncertaintywith recourse. The key contribution of our approach is thederivation of the optimal policy for body biasing as an affinefunction of the realizations of the uncertain parameters (gatelength, L , and threshold voltage, Vth ). The solution to the aboveoptimization problem therefore yields the sizes for the gates in thecircuit and an optimal body bias policy.2. DESIGN-TIME / POST-SILICON COOPTIMIZATION: MOTIVATION ANDCHALLENGESThe central problem of statistical optimization methods isreducing the dual parametric yield loss due to power and timingconstraints. This is because power consumption has become theyield-limiting factor, indirectly affecting the achievable maximumclock frequency [17]. In the absence of substantial leakagepower, parametric yield is determined by the maximum possibleclock frequency. When realistic leakage power numbers forcurrent CMOS technologies are added, the total power startsapproaching the power limit determined by the cooling andpackaging considerations. Crucially, the exponential dependenceof leakage on process spread will mean that the total power willcross the cooling (power) limit well below the maximum possiblechip frequency, since chips operating at higher frequencies haveexponentially higher leakage power consumption. Due to theinverse correlation between speed and leakage, yield is limited3. GATE AND CIRCUIT MODELINGAdjusting the circuit properties to manufacturing conditions canbe achieved by several techniques, including adaptive buffer20

sizing, adaptive body biasing, and adaptive supply voltagebiasing. Because joint timing-leakage optimization is of primaryconcern, adaptive body bias may be the most useful tool. It hasbeen demonstrated [7, 11] that body biasing can be employed asan extremely effective knob to perform post silicon optimizationand performance tuning by reducing the leakage for those diesthat violate power constraints and increasing the frequency ofthose dies that do not meet delay specs.The adaptive body bias technique exploits the dependency of thethreshold voltage of a MOSFET device on its source-to-bodyvoltage to achieve dynamic tuning of its delay and leakage power.For an NMOS device, the threshold voltage can be expressed as[18]:Vth VthO Y(VSB 2Xfcaptured using a first-order parametric delay model:(L, Vth, VSB )Using a modeling approach similar to [20], the subthresholdleakage current of a gate is expressed as an exponential functionof the random parameters as:Idi a',- ai2wUa3EwkVlI C 10 exp(aAL bA Vth cA VSB)(4)where 10 is the nominal value of leakage per unit width. Weobtain a good fit using this model (Figure 1), the rms error being88%. For a circuit block the expression for leakage can beexpressed as:bf)m](3)where AL and A Vth are the parameter deviations and A VSB isthe applied body bias. The sensitivities are the first-orderderivatives of delay with respect to the specific variablewhere VthO is the threshold voltage of the device with zero bodybias, -y is the body bias coefficient, and Of is the Fermipotential. Decreasing the source potential relative to the body ofan N-channel device, translates to a negative VSB, and decreasesthe threshold voltage. This technique, known as forward bodybiasing (FBB) reduces the delay of the gate at the expense ofleakage power. On the other hand, application of reverse bodybias (RBB) by applying a positive VSB causes the thresholdvoltage of the device to increase. RBB is thus very effective inreducing the leakage power consumption [1].The need to setup a rigorous statistical optimization problemunder uncertainty requires us to use approximate, linearized delaymodels, such as a piecewise delay of [19]. Let the gate delay berepresented as d, d, Ad1, where d, is the nominal gatedelay and Adi is the term representing the variability in delay.The dependence of nominal gate delay on gate sizes can bedescribed by the piecewise linear equations: SIAL S2A Vth S3A VSBAdItotw1i .exp(aiALi biA Vth,i CiAVSB) Epwhere the nominal gate leakage is1o,i pi wi.Following [21], we assume that the impact of random componentof variation on chip-level leakage value can be captured by aconstant multiplier that we take to modify the value of ,i, in theabove expression.The essence of adjustable optimization framework is that thevariable that is allowed to be tuned is not determined arbitrarilybut is dependent in some way on the realizations of uncertainvariables. As was mentioned before and will be justified in thenext section, a computationally tractable solution to a statisticaladjustable problem requires that A VSB be an affine function ofuncertain parameters, L and VthA VSB(1) 7TO 7FIALg 7W2A Vth,g(5)Here, the coefficients 7w0, 7rI and 7w2 are to be determined in theprocess of optimization. Such a parameterization is physicallyequivalent to compensating for the variation in leakage due to Land Vth, by applying body bias [22]. Though, the value of bodybias is not a random variable, based on (5), it can be treatedmathematically as one. With that observation, let us define:where m is the number of fitting regions I and ais are the fittingcoefficients. This model captures the dependence of delay on thesize of the gate width wi, and its load E wk The accuracy of theapproximation is reasonable: the average error is less than 5% form 3. The size range considered is 1-8x of the minimum sizegate.Analytical models are used to relate the impact of variabilitysources on power and delay. The variability is assumed to comefrom two major sources. Transistor gate length (L ) exhibitsstrong lithography induced variability. Threshold voltage (Vth )variation due to oxide thickness and dose variation is also takeninto account. The impact of L on Vth due to drain-inducedbarrier lowering is predicted by the device model directly, whichpermits modeling L and Vth as independent random variables.Both L andVth are assumed to follow the normal distribution.An additive statistical model that decomposes the variability, ofboth L andVth, into the global (chip-to-chip) and local (intrachip) uncorrelated variability components is used. For gate length:L Lo ALg ALi(2)65.00EELO4-3-02(U-Jdo1-uJR01234567Leakage from SPICEFigure 1. Comparison of the normalized leakage ofinverter predicted by SPICE and the analytical leakagemodel.The impact of process parameter variability on gate delay is21

N(ti, oi2) aiALg biA Vth,g CiA VSBThe mean and variance of a lognormal Y ex in terms of themean and variance of the normal random variableX N(,u 2 ) are [23]:Ximin{c (v :V(( -[U,V,b,c] C Z) E(Y) Var(Y)exp(u exp[2(u2) u2)]-exp(2,u u2)(7)w exp(aiALg biA Vth,g CiA VSB))ZE(i .wivand ,E( a-ALg b,A Vth,g C-A VSB) wTOwe can write the expected value of total block leakage as:iE(Itot) i *exp(wo /2)wi(8)(10)Still, it is shown in [16] that the general robust problem withadjustable parameters is NP-complete, unless restrictions areapplied on how exactly the adjustable variables tune themselvesto uncertain data. It is shown that a computationally feasibleadjustable robust linear problem can be achieved if the adjustablevariables are constrained to be affine functions of the uncertainvariables. This is equivalent to:Observing that:E(ItOt)b}In this formulation, the adjustable variables v are allowed todepend on the realization of ( .(6)2v: Uu Vv w W(From this we see that the adjustable variables can be tuned oncethe realization of uncertain data is known. However, if we are tobe able to identify an optimal policy and do that computationallyefficiently, the dependency cannot have general form, but must beconstrained. This ultimately leads to the affinely adjustable robustlinear program84. DESIGN TIME / POST SILICON COOPTIMIZATION ADAPTABLE ROBUSTOPTIMIZATIONmin{c(TIn the optimization strategy we develop, the optimal body bias isdetermined after the realization of uncertainty of the processparameters. On-chip measurements are used to measure the actualparameter values and their deviations from nominal values. Then,the policy derived during optimization can be used to choose anoptimal forward or reverse body bias. RBB can be applied toreduce yield loss in the high frequency (high leakage bins), andcan be used with FBB to tighten the distribution at the lowfrequency bins.) :Uu V(w W()v bV [U, V,b,c] E Z}(11)In particular, for uncertainty sets specified using linear or secondorder cone constraints, the above problem can be reformulated asan LP or a second-order conic program respectively [16].4.2 Co-Optimization: Problem FormulationWe now map our design-time and post-silicon tuning probleminto a robust adjustable linear program. Our objective informulating the problem

sizing, adaptive body biasing, and adaptive supply voltage biasing. Because joint timing-leakage optimization is ofprimary concern, adaptive body bias may be the most useful tool. It has been demonstrated [7, 11] that body biasing can be employed as an extremely effective knob to perform post silicon optimization and

Weasler Aftmkt. Weasler APC/Wesco Chainbelt G&G Neapco Rockwell Spicer Cross & Brg U-Joint U-Joint U-Joint U-Joint U-Joint U-Joint U-Joint U-Joint Kit Stock # Series Series Series Series Series Series Series Series 200-0100 1FR 200-0300 3DR 200-0600 6 L6W/6RW 6N

REFERENCE SECTION NORTH AMERICAN COMPONENTS John Deere John Deere Aftmkt. John Deere APC/Wesco Chainbelt G&G Neapco Rockwell Spicer Cross & Brg U-Joint U-Joint U-Joint U-Joint U-Joint U-Joint U-Joint U-Joint Kit Stock # Series Series Series Series Series Series Series Series PM200-0100 1FR PM200-0300 3DR

American Legion 5th District 5th District Commander, Western Springs Cicero Post #96 DesPlaines Post #36 George L. Giles Post #87, Chicago Maywood Post #133, Melrose Park Morton Grove Post #134 Schiller Park Post #104 T.H.B. Post #187, Elmhurst Edward Feely Post #190, Brookfield Richard J. Daley Post #197, Chicago

Bones and Joints of Upper Limb Regions Bones Joints Shoulder Girdle Clavicle Scapula Sternoclavicular Joint Acromioclavicular Joint Bones of Arm Humerus Upper End: Glenohumeral Joint Lower End: See below Bones of Forearm Radius Ulna Humeroradial Joint Humeroulnar Joint Proximal Radioulnar Joint Distal Radioulnar Joint Bones of Wrist and Hand 8 .File Size: 2MBPage Count: 51

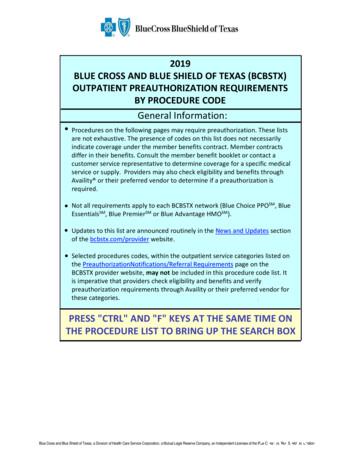

Procedure Code Service/Category 15824 Neurology 15826 Neurology 19316 Select Outpatient Procedures 19318 Select Outpatient Procedures 20930 Joint, Spine Surgery 20931 Joint, Spine Surgery 20936 Joint, Spine Surgery 20937 Joint, Spine Surgery 20938 Joint, Spine Surgery 20974 Joint, Spine Surgery 20975 Joint, Spine Surgery

Procedure Code Service/Category 15824 Neurology 15826 Neurology 19316 Select Outpatient Procedures 19318 Select Outpatient Procedures 20930 Joint, Spine Surgery 20931 Joint, Spine Surgery 20936 Joint, Spine Surgery 20937 Joint, Spine Surgery 20938 Joint, Spine Surgery 20974 Joint, Spine Surgery 20975 Joint, Spine Surgery

Question of whether density really improved Also constructability questions INDOT Joint Specification Joint Density specification? More core holes (at the joint!) Taking cores directly over the joint problematic What Gmm to use? Joint isn't vertical Another pay factor INDOT Joint Specification Joint Adhesive Hot applied

To create a corner post, install the 900 profile over the face of the post, for the new run of fence, and insert a post infill over the exposed recess of the corner post. 2420mm post face to post centre HOUSE 1 HOUSE 2 5mm clearance minimum 90º 90 configuration Insert post infill Install 90º profile over the face of the mid-post.